基于NCO IP core的Chirp函数实现设计

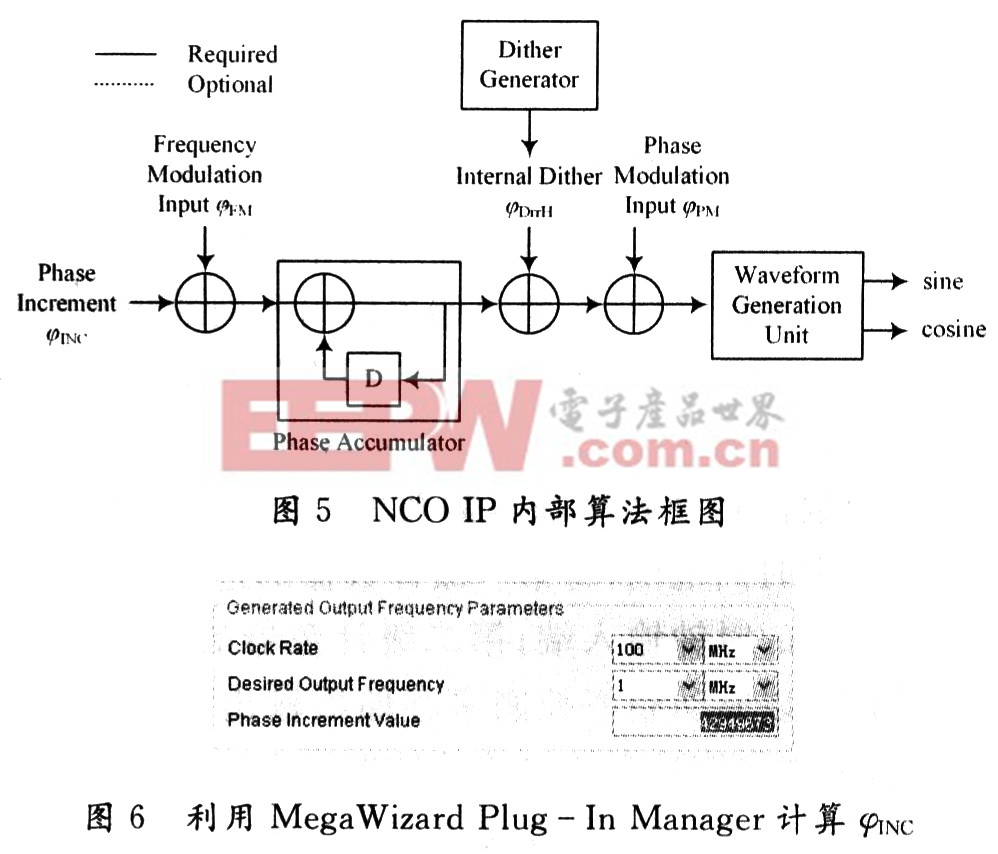

数字压控振荡器知识产权核(Numerically Con-trolled Oscillators Intellectual Property Core,NCO IPCore),通过多种算法(相位累加或者CORDIC算法,在此不一一赘述),实现了一个离散幅度和时间的正弦波信号输出。输入控制字和输出频率之间满足以下方程:

s(nT)=Asin[2π(f0+fFM)nT+ψPM+ψDITH)] (5)

式中:T为该模块的工作时钟;f0是由输入频率控制字ψINC决定的初始频率;fFM是由调制频率控制字ψFM决定的调制频率;ψPM为该输出正弦波的调制相位,ψPM=P/2Pwidth,由输入控制字P的比特位数(Pwidth)决定了它的精度;ψDITH为模块内部自身的不稳定而引起的相位杂散(噪声);幅值量A=2N-1,其中N为幅值精度取值在4~32之间。

该设计中仅采用通过改变频率控制字ψINC,以实现改变频率输出的目的,为此式(5)可以简化为:

式中,f0由给定的频率控制字ψINC决定,满足如下方程:

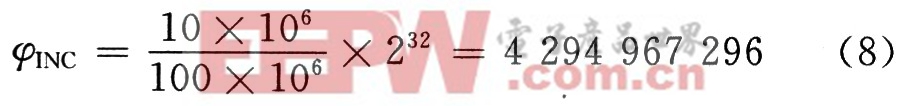

式中:M为累加器精度;fclk为该模块的输入时钟频率,单位为Hz。例如:在fclk=100 MHz的情况下,如果需要f0=10 MHz的输出,ψINC的计算如下:

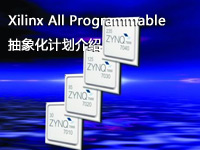

通过Altera公司的FPGA编程软件QuartusⅡ提供的MegaWizard Plug-In Manager功能,在NCO IPCore参数配置中自动对ψINC的计算,很容易得出在输入频率的条件下所需输出频率的ψINC(累加器精度为32 b的情况下)如图6所示。

本文引用地址:http://www.eepw.com.cn/article/188505.htm

值得注意的是:在MegaWizard Plug-In Manage中,ψINC的精度只保留到了百位。

评论