引脚电容在引脚上耦合的噪声电压

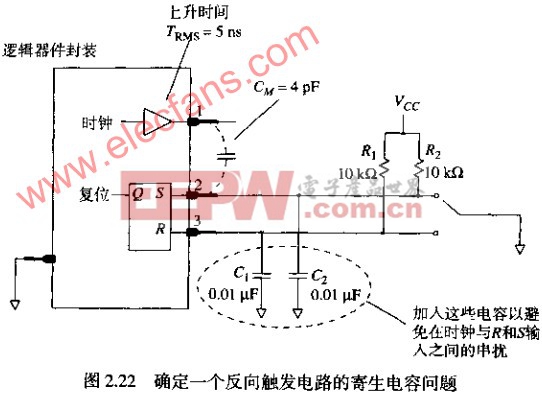

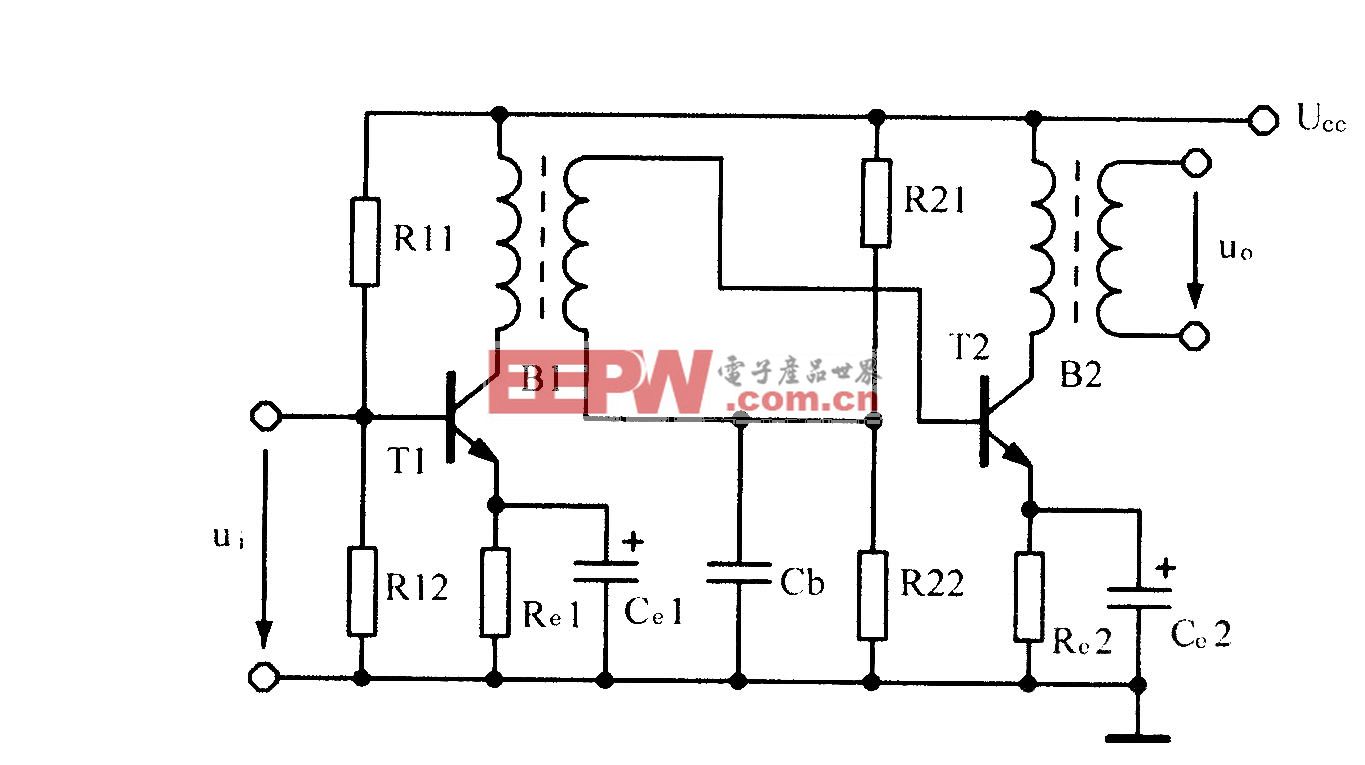

逻辑器件相邻引脚之间的寄生电容能够在敏感的输入法引脚上耦合出噪声电压。图2.21描述了一个互容CM使得逻辑器件中引脚1和引脚2产生耦合的情形。

本文引用地址:https://www.eepw.com.cn/article/187937.htm

可以用式:![]() 计算由电路1传入电路2的串扰百分比:串扰=R2CM/T10%-90%

计算由电路1传入电路2的串扰百分比:串扰=R2CM/T10%-90%

其中,CM=4PF(电路1和2的互容)

R2=37.5欧(75欧长传输线与75欧端接器的并联阻抗)

T10%-90%=5NS(引脚1上信号的电压上升时间)

在本例中,串扰为0.03(3%)

当上升时间变得越短时,容性串据的问题变得越来越严重。同时,当连接的输入阻抗更高时情况也随之变得更差。

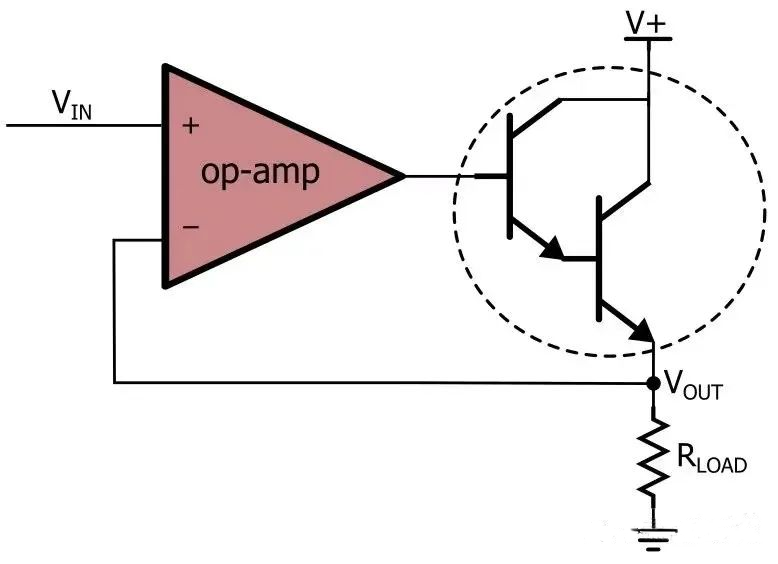

图2.22说明了高阻抗输入的问题。图2.22中的ASIC器件产生一个时钟信号,同时也反向触发一个开关输入。没有C1和C2时,R1和R2的阻抗非常高,这总味着实际上来自引脚1的全部时钟信号都将会在引脚2上出现。

高频时电容器C1和C2降低了接收电路的阻抗,阻止了容性串扰问题的产生,对于接收电路中的容性负载,串扰的百分比正好等于电容的比值:串扰=CM/C1

C1设定为0.01UF时,得到的串扰只有0.0004,这一量级的串扰是无关紧要的,检查R1、C1的时域响应,得到时间常数为0.1MS。没有谁能够分辩出这一微小的差异。

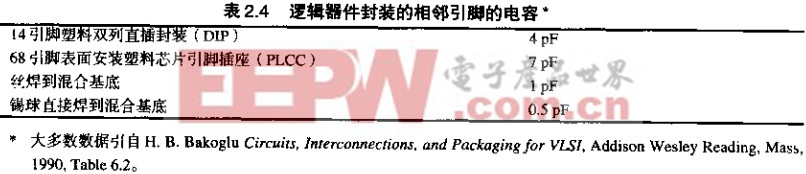

表2.4按大小次序列出了各种封装中相邻引脚之间的电容值。

评论