高速AD测试中的难点

高精度ADC的采样率不高,测试关键是要有高精度的信号源。而高速ADC测试是一项更具挑战性的工作,其中采样时钟的Jitter和高速数字接口是两个必须面对的难题。

采样时钟的Jitter(抖动)问题

随着输入信号和采样频率的增大,ADC的采样时钟所携带的Jitter,在很大程度上影响到测试结果,使之成为一项很艰难的工作。这中间有两个重要的关系需要考虑,第一个重要的关系见图1的推导。

这是在暂不考虑量化误差的情况下,ADC的采样时钟所携带的Jitter与ADC信噪比之间的关系。这一关系也表明ADC的信噪比会受采样时钟Jitter所限。公式推导中,在计算采样误差幅度时,选取了t=0的时刻,因为此时正弦信号的斜率最大,得到的采样误差最大。表1是由式1得到的结果,从中可以看到,被测试的输入信号频率越大,对信噪比的要求越高,则对采样时钟Jitter的要求越苛刻。如输入信号是50.1MHz的正弦波,在不考虑量化误差的情况下,信噪比要测到55dB,则要求采样时钟的Jitter不能大于5.649140981ps。如果再考虑量化误差的带来的影响,则需要更小的Jitter。

时钟Jitter并不是高速ADC性能的唯一限制。需要考虑的第二个重要的关系是ADC的分辨率与信噪比之间的关系,

即SNR=6.02×Bits+1.76——(2)

这是从量化噪声方面考虑得到的公式,由它可以计算理想ADC信噪比的理论上限。

综合考虑以上两点,再加上DNL和热噪声的因素,得到以下的简化公式。

式中第二项表示除采样时钟Jitter之外的因素,包括量化噪声、DNL和热噪声,N代表ADC的位数。由这个公式,可以计算出测试ADC时所能容忍的采样时钟的最大Jitter。具体的做法是,输入很低频率的信号,做一次SNR测量,使得式3中第一项可以忽略不计,从而得到ε的值。然后根据ε和芯片可能达到的SNR,再次利用此公式,去计算出能允许的采样时钟的最大Jitter,从而判断测试系统,例如ATE设备提供的时钟,是否能够满足测试要求。

ADC高速接口问题

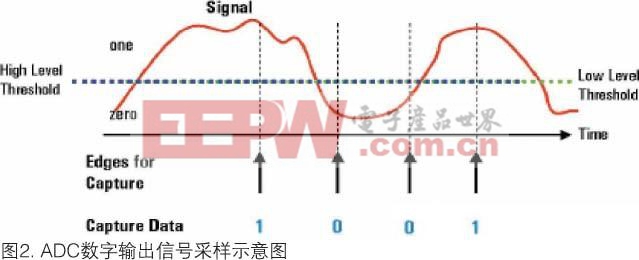

伴随ADC向高速发展的趋势,其数据输出速率也越来越高(图2)。在多通道ADC中,由于采用并行转串行的技术,会要求更高的数据传输速率。目前高速ADC一般采用高速、低摆幅的差分信号输出,如LVDS和SLVS。怎样才能准确无误地接收到这些高速,低摆幅的信号,是高速ADC测试所要解决的另一个重要问题。

由于输出信号摆幅低,如LVDS,单端摆幅只有350mV,如果测试所用的ATE设备以单端信号的方式,分别对两路差分信号进行采样,由于这种方法破坏了差分信号的抗干扰结构,再加上信号速度高,使得采样时ADC的输出信号很容易被环境噪声所淹没,出现误码。所以这时就要求ATE设备在采样通道中,集成有真正的差分比较器,以保证采集这种低摆幅差分信号的正确性。

评论