怎样才能充分利用低压差分信号LVDS

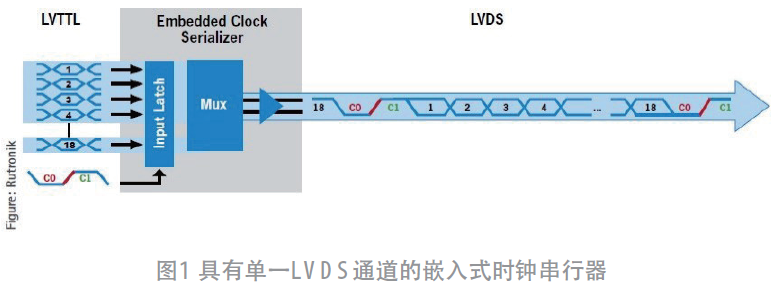

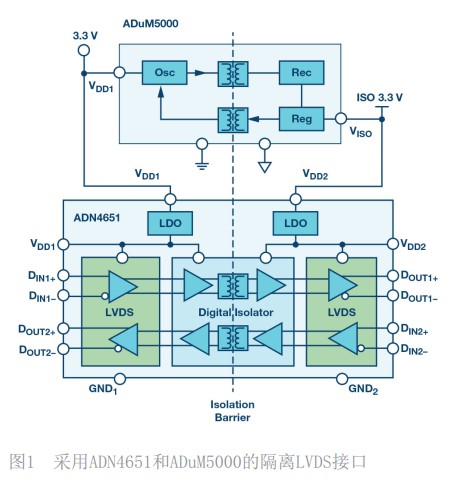

低压差分信号(LVDS)是一种低压、差分信号传输方案,主要用于高速数据传输。根据 ANSI/TIA/EIA-644 规范中的定义,它是一种最为常见的差分接口。这种标准只对适合于 LVDS 应用的驱动器和接收机电气特性进行了规定。因此,它只是一种电气标准,常被一些更高级的协议标准当作其接口或物理层。

本文引用地址:https://www.eepw.com.cn/article/186628.htm在高速模拟数字转换器(ADC)中使用该传输方案可在保持转换器高性能的同时实现高速数据输出。独立 ADC 必须能够驱动以PCB走线形式存在的容性负载、以及接收电路的输入逻辑。此处,ADC 输出级的一个单端驱动器会导致大量瞬态开关噪声,这些噪声是由大电流晶体管的开和关造成的。这些瞬态会耦合回ADC的模拟前端,从而对其性能产生不利影响。

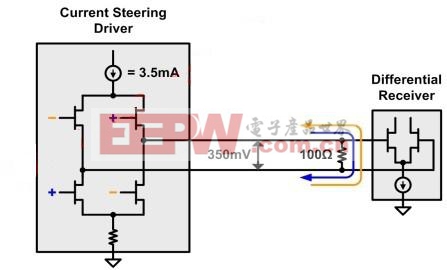

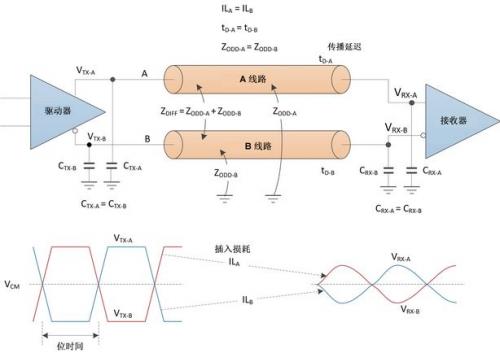

然而,LVDS 驱动器级需要在一个始终开启的 3.5mA(典型值)电流源环境中运行(请参见图 1)。通过差分对导体以不同方向重新分配电流,便可形成总线上的逻辑 1 和 0。这种消除开关噪声和 EMI 的“始终开启”特性正是降低 ADC 性能的主要原因。

图 1: LVDS 驱动器和接收器。(电流型驱动 差分接收器)

由于专为点对点信号传输而设计,LVDS使用的是一种简单的端接方案。安装在接收器输入端的单个100欧姆电阻端接差分对,从而消除了反射。

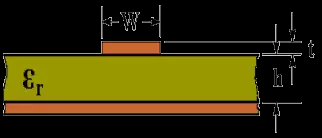

由于高阻抗接器输入,驱动器电流源的全部电流流经端接电阻,从而产生了一个 350 mV 额定值的低、差分总线电压。该电压在 1.2 V 共模电位左右摆动,其为典型驱动器输出失调电压(请参见图 2)。

图 2:LVDS 总线电压电平。

相比单端方案,差分信号传输还有另一个 LVDS 好处,因为它不易受到共模噪声的影响,并且产生更少的电磁干扰 (EMI)。

由于接收器只响应差分电压,因此同邻近的信号线耦合的噪声被接收器视作共模调制,从而被拒绝接收。另外,由于两个差分对导体传导电流相等但极性相反,因此它们的磁场基本互相抵消,从而实现 EMI 最小化。

根据数据速率的不同,标准 LVDS IC 可以驱动长达 10 米的距离。然而,不应强制高性能ADC驱动这一距离。取而代之的是,建议使用两英寸以内的较短的输出线,以防止邻近电路的噪声耦合到 ADC 输出端,因为其可能会反馈耦合至 ADC 模拟输入端。

尽管低功耗、低 EMI 和高噪声抗扰度使得 LVDS 成为高速数据转换器的接口选择,但是必须运用精心的布线技术,以避免阻抗不连续和信号时延差,否则就抵消了上述 LVDS 的好处。

评论