适用于平板显示器的HV632解析方案

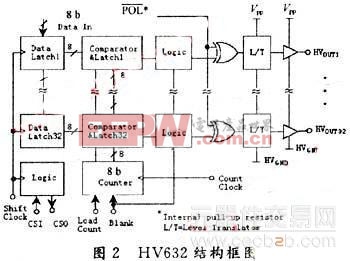

HV632的结构框图如图2所示。根据结构图简述其工作原理:8位二进制总线数据通过D1~D8口输入到Data Latch(数据锁存器)中,在移位时钟(Shift Clock)的上下沿分别进行锁存,每16个Shift Clock脉冲为一组,因此可以锁存32个8位二进制数据,在第一个Shift Clock脉冲的上升(或下降)沿读入的数据锁存到Data Latch1,并与高压输出HVout1相对应,依此类推,最后一个8位二进制数据锁存到Data Latch32中,并与高压输出HVout32相对应。每一个数据锁存器锁存的数据都会在Comparator(比较器)中与8 B Counter(8位计数器)的输出进行比较,当锁存器中的数据与8位计数器的输出相匹配时,高压输出HVout跳变。因为该8位计数器是一个可逆计数器,所以在一个完整的可逆计数周期内,会有两次相匹配的情况,随着D~D8输入的不同,输出的脉冲宽度会随之改变,从而达到脉宽调制的作用。

Logic部分

图2所示的HV632结构框图中含有2个Logic部分,其中一部分指的是连接比较器和异或门的逻辑部分,该部分的电路实际上就是一个带有置位功能边沿的D触发器,置位信号通过BLANK作用,BLANK为高时,高压输出全为低电平。另外,BLANK在计数器中也有作用,因此,在介绍该芯片引脚功能时指出,BLANK信号具有重置计数器和高压输出的功能。Logic的另一部分指的是连接有输入信号CSI和Shiftclk,输出信号CSO的部分。该电路的作用就是实现片选信号的输入与输出,每一个输入信号CSI脉冲的到来,都会产生一个片选输出脉冲,每一个CSI和CSO信号之间都相隔16个Shift Clock脉冲,又因为Shift Clock是双沿触发,从而在一组CSI和CSO信号之间能够读入32个8位二进制数据,实现32通道的输出。该结构的仿真波形如图3所示。

高压输出部分

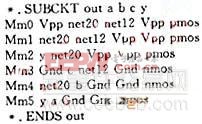

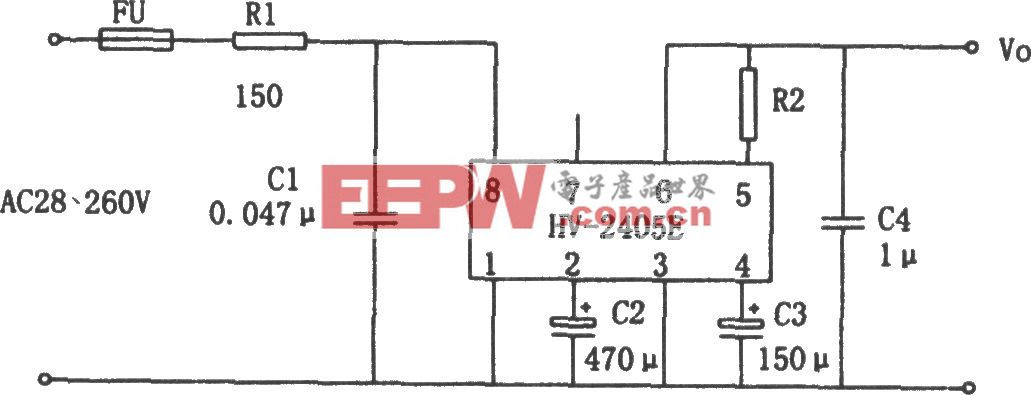

高压输出部分实现了低压驱动高压,其电路是模拟的,因此,利用Spice语言进行了描述和模拟,最终结果显示,该电路确实实现了低压驱动高压。其结构利用Spice语言描述如下:

仿真结果见图4。

输入信号存在这样的逻辑关系A=C=~B,这是由和该结构相连的前一个逻辑结构的输出决定的,3个输入信号的电位最高均不超过5 V。由图可以看出,当A为高电平时,输出Y=0;当A为低电平时,输出Y=Vpp,Vpp为80 V高压,由此实现了低压驱动高压。

其他部分

Data Latch(数据锁存器)采用由二选一选择器组成的边沿D触发器实现数据锁存:在CP的下降沿到来时,输出Q随着输入D的变化而变化;在CP的上升沿到来时,起到锁存作用。该数据锁存器结构简单,便于集成。

8b Counter(8位计数器)是一种以二选一选择器组成的触发器作为其主体、带有加减控制模块的单时钟结构8位可逆计数器,具有异步置位功能。其置位信号就是BLANK,高电平有效。

评论