高级动态性能模数转换器简介

ADC12C/DSxxx与ADC14C/DSxxx

ADC12C/DSxxx和ADC14C/DSxxx系列模数转换器内置高性能的采样及保持放大器和高精度带隙电压参考电路,输入带宽高达1GHz,因此可以支持中频采样工作。此外,这系列芯片输入方面有单及双通道,而输出方面有并行CMOS及串行LVDS可供选择,更容易将FPGA或ASIC与模拟/数字转换器连接一起。这系列芯片的各型号产品都引脚兼容,确保系统可以轻易由12位升级至14位,部分芯片更可在摄氏-40至+85℃的广阔工业温度范围内工作。单通道的型号采用32引脚的LLP封装,尺寸5mm×5mm,而双通道的型号则采用60引脚的LLP封装,尺寸9mm×9mm。

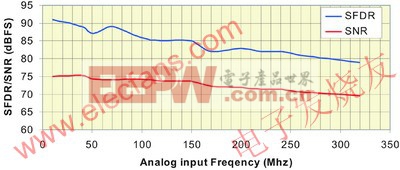

这系列模数转换器若以1GHz以上的满功率带宽工作,则具有优良的动态性能及线性度,功耗较低。这系列芯片若以高达300MHz的输入频率工作,其无杂散信号动态范围(SFDR)可高达80dB。若采用3.0V的供电电压,其功耗更低至320mW。即使输入频率超过300MHz,信噪比仍然高达70dB以上,让系统设计工程师可以充分利用这个低噪声的优点,改善移动电话基站的接收能力。由于这系列芯片具有高带宽及高采样率的优点,因此可以支持高中频采样。换言之,系统无需加设下变频级,为系统节省可观的成本,而且低功耗的特点也令系统更稳定可靠。最后要强调的一点是,这系列芯片的带宽很高,因此驱动器放大器不会受太多的限制,让工程师可以精简信号路径的滤波系统。

若模拟输入频率较低,则以80MSPS的采样率工作,其信噪比可达75dBFS, SFDR可达90dB,有效位数(ENOB)12位。若采样率为105MSPS,信噪比可达74.5dBFS,SFDR可达90dB,ENOB可达11.9位。至于直流电方面的表现,这系列模数转换器的输入偏移误差±1mV,增益误差±0.5%FS,微分非线性(DNL)误差±0.5LSB,而积分非线性(INL)误差±1.5LSB。由于这系列芯片采用先进电路设计,因此功耗可降至最低,实际功耗则取决于工作频率。由于时钟输出引脚的上升边缘位于输出信号眼图的中央位置,因此系统设计工程师可以利用时钟输出引脚捕捉并行的CMOS输出数据。

高速传输的解决方案

ADC14C105双通道模数转换器可将两条通道的不同参数互相对准,在对准过程中,芯片先将所取得的CMOS时钟输入传送到芯片的核心,然后由一条缓冲通道再将时钟输入传送到双通道的时钟输入端,整个过程只需4个CMOS栅极。此外,芯片内部区段分隔及供电路径极为匹配,使通道间的孔径抖动失配不超过30fs,而通道间的孔径延迟失配则不超过50ps。此外,这款双通道模数转换器的通道间增益误差失配不超过±0.2%FS,偏移失配不超过±1mV,而通道间的串音干扰则达到-95dB以上。

图1 ADC14C105以105MSPS采样率工作时,信噪比及无杂散信号动态范围的频率变化

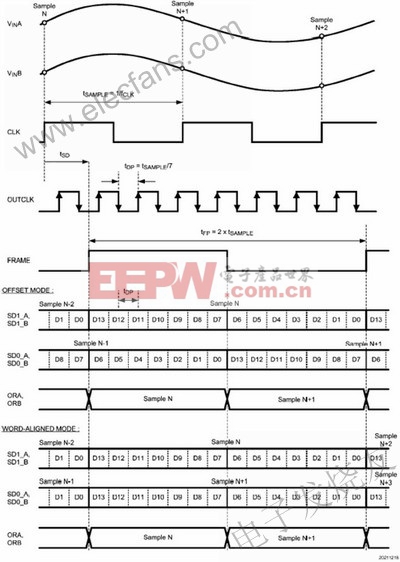

LVDS是个电磁干扰极低的接口解决方案,最适用于高速的数据转换器,已成为高速数据传输的标准接口。串行LVDS输出模数转换器设有单线及双线两种不同的数据传输模式,这种设计的目的是要降低LVDS数据传输率一半。单线模式适用于25MSPS至65MSPS的范围,这个范围内的采样率相当于350Mbps至910Mbps的数据传输率。双线模式的数据传输率刚好是上述传输率的一半,因为LVDS输出引脚的数目增加了一倍,因此,LVDS模数转换器若采用双线模式工作,转换率便可提高到50MSPS至105MSPS的范围内。

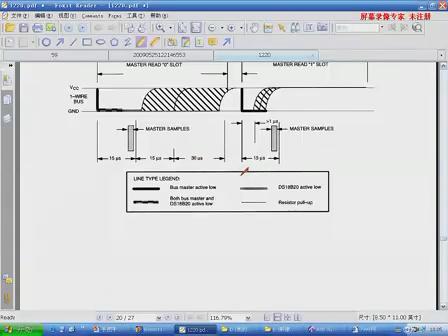

LVDS接口设有偏移模式和字对准模式两种不同的数据捕捉方式,以便解串器更易捕捉数据,用户则可按照个别应用的需要,选用适合的数据捕捉方式。正如图2的数据所显示,SD0/SD1两条通道采用字对准的模式作为预设模式。若采用偏移模式,SD0通道的数据比SD1通道的数据延迟半个字。换言之,加设双线模式这一选项可以精简高速数据传输系统的设计流程,使工程师的设计工作变得更为容易。

图2 双线模式的定时时序图

评论