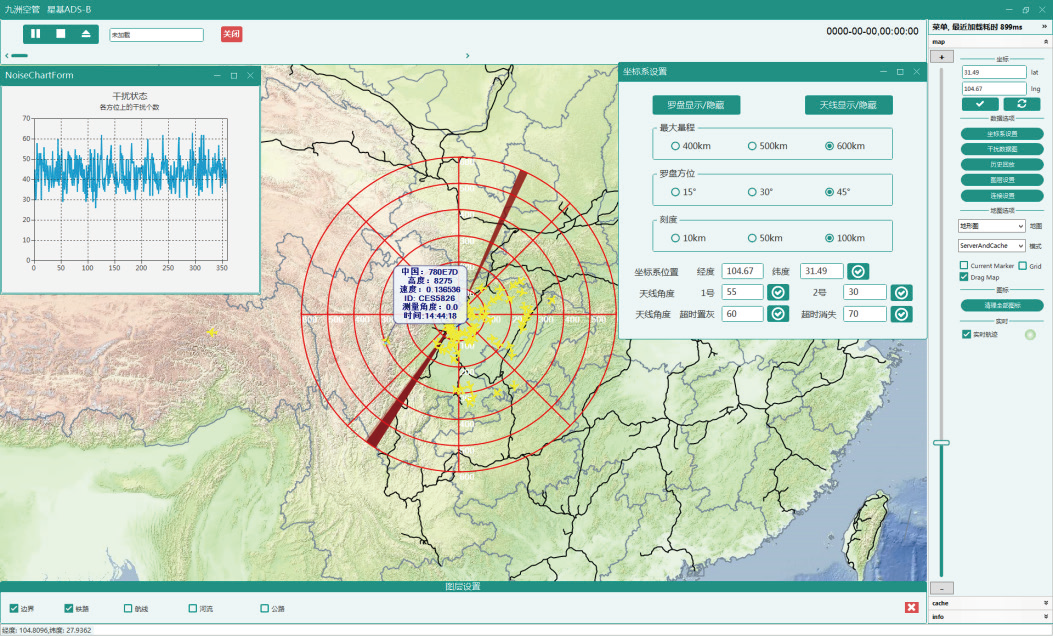

基于ADS的接收机码元同步算法实现

0 引言

在数字接收机中,为了在抽样判决时刻准确判决发送过来的码元,需要提供一个确定抽样判决时刻的定时脉冲序列。这个定时脉冲序列的重复频率必须与发送的数码脉冲序列一致(即接收、发送双方必须同步,具有相同的主频率),同时在最佳判决时刻对接收码元进行抽样判决。这样的定时脉冲序列称为码元同步。

16QAM(Quadrature Amplitude Modulation)接收机要完成16QAM信号的解调首先要完成码元同步,再通过随后的均衡、载波恢复等模块完成信号的解调。因此码元同步算法的实现是至关重要的一部分。

1 码元定时同步原理及其在ADS中的设计

数字化的解调器中,经过下变频所得的基带信号通过匹配滤波器,然后以时钟周期为Ts的固定采样频率进行采样、量化后进入码元同步环路。

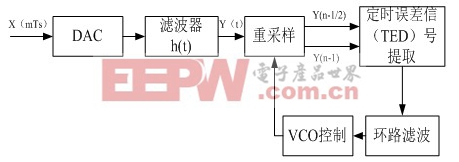

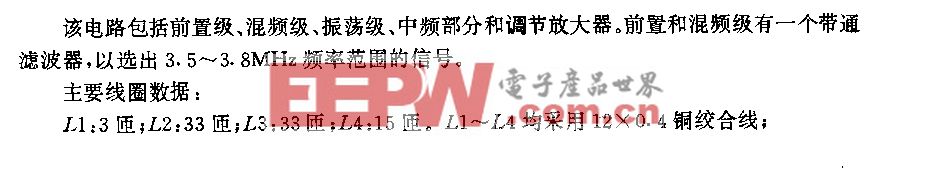

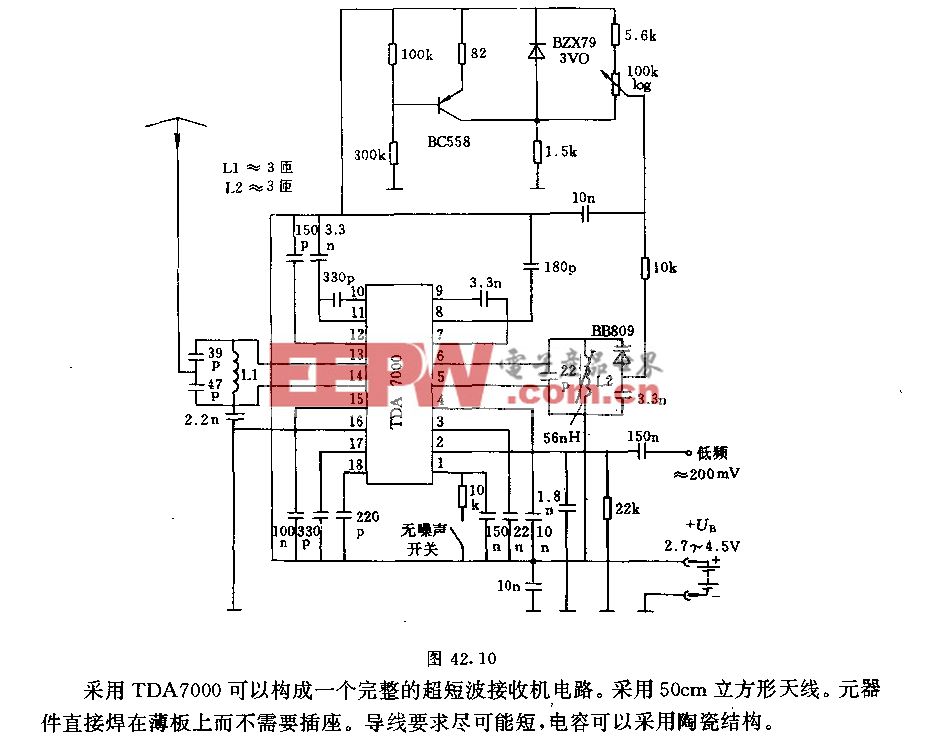

图1 码元同步模块的结构

在论文中,具体采用的定时同步模块如图1所示,它由内插滤波器(由DAC、滤波器和重采样等效实现)、定时误差提取(TED)、环路滤波器以及VCO控制器组成。从图中可看出:信号经过内插后,每个符号内有两个采样点,再进行时钟误差提取,得到的误差信号经过环路滤波器后送给VCO,最后控制内插完成同步。即通过采样点提取时钟控制信号调整采样时钟来达到同步。

下面分别介绍各模块的原理。

1.1 内插滤波器原理

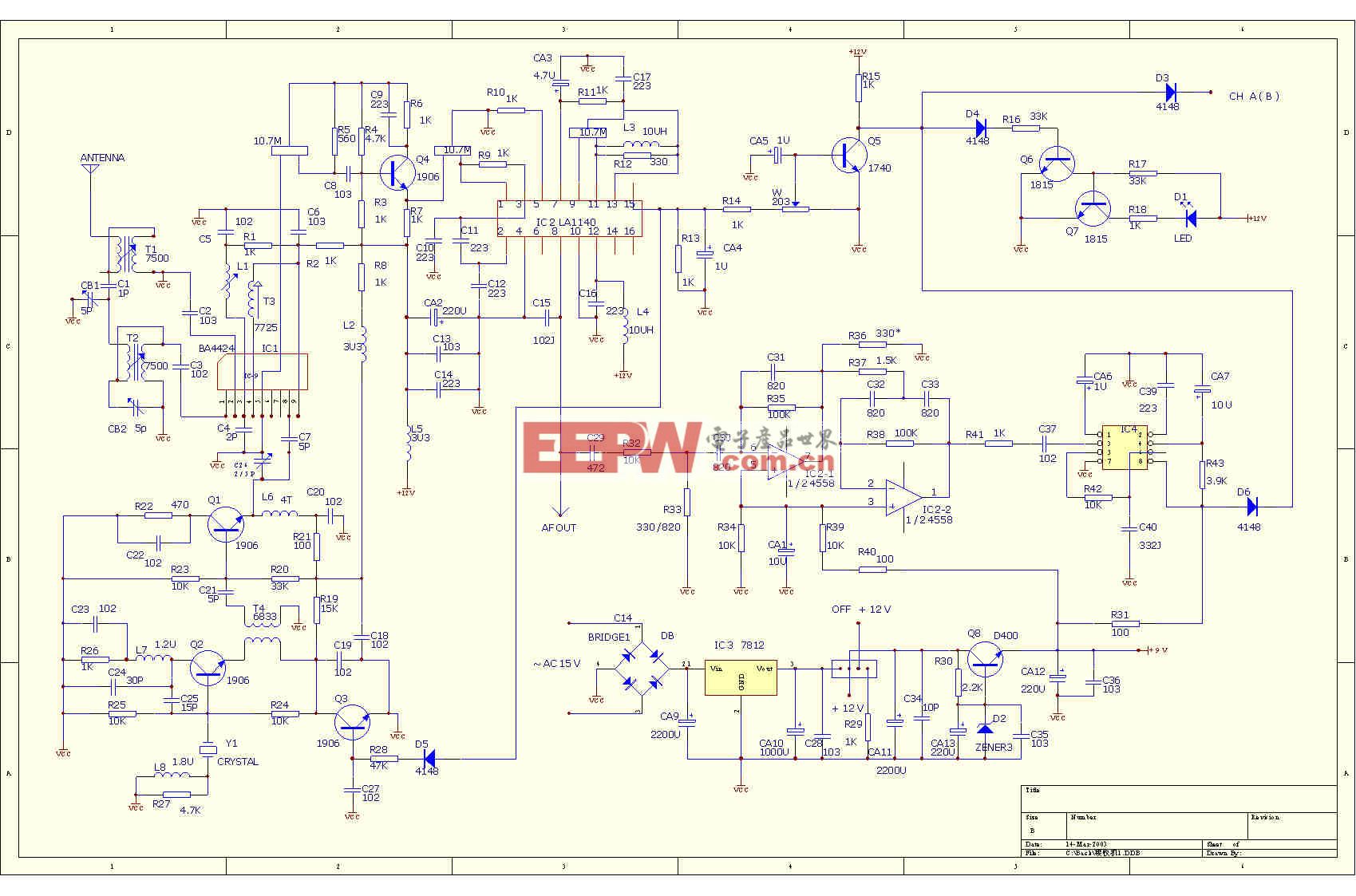

内插滤波器实际上实现的是一个数据的速率转换可以假设它的模型如图2所示。

图2 速率转换

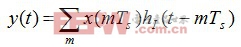

假定接收端固定采样时钟为 ,符号周期为T。内插器接收的信号为

,符号周期为T。内插器接收的信号为 ,通过DAC及滤波器后

,通过DAC及滤波器后 ,得到一个连续时间的输出:

,得到一个连续时间的输出: (1-1)

(1-1)

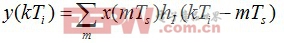

现在,对于y (t),在每个时刻 时对其再次进行采样,其中,k为正整数。T为内插器周期,它与符号周期是同步的。

时对其再次进行采样,其中,k为正整数。T为内插器周期,它与符号周期是同步的。 (1-2)

(1-2)

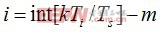

对于上式(5-2),m为输入序列指针,定义滤波器指针为: (1-3)

(1-3)

同样,定义基本指针为: (1-4)

(1-4)

分数间隔为: (1-5)

(1-5)

内插公式可以重新写为: (1-6)

(1-6)

式(1-6)为数字内插滤波器的基本方程。

引入参数 ,

, 是有实际意义的。它们表示了

是有实际意义的。它们表示了 ,

, 之间的调整关系。其中,

之间的调整关系。其中, 决定了计算第k个内插值

决定了计算第k个内插值 的N=N2-N1+1个信号样值,

的N=N2-N1+1个信号样值, 指示了内插估值点,并决定用来计算内插值

指示了内插估值点,并决定用来计算内插值 的N个插值滤波器脉冲响应样值。一般情况下,

的N个插值滤波器脉冲响应样值。一般情况下, 是个无理数且对每次内插都是变化的,直到定时稳定时,

是个无理数且对每次内插都是变化的,直到定时稳定时, 将稳定在某一个定值上。

将稳定在某一个定值上。

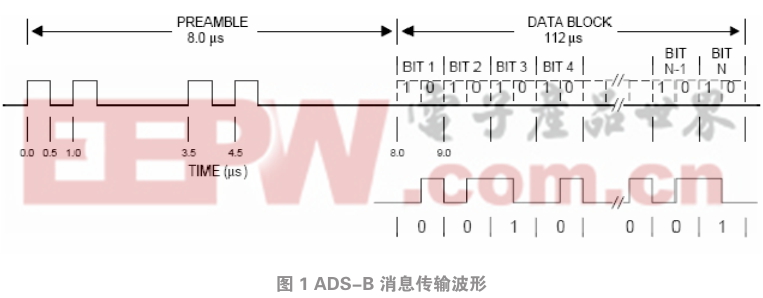

1.2 定时误差(TED)信号的提取

Gardner 码元同步算法是一种异步时钟恢复方法,本地生成码元时钟,采用插值方法得到抽样时刻码元值,不需要满足采样时钟与码元时钟是整数倍关系的要求。 Gardner码元同步算法中,输入的基带信号经过插值后得到2倍码元速率的抽样数据,抽样数据经过反馈支路控制数控振荡器输出频率从而调整码元时钟,采样得到最佳采样点,完成时钟的锁定和跟踪。

Gardner算法不需要判决反馈,每个数据需要两个采样点,其中一个是strobe点,即符号最佳观察点;另一个是midstrobe点,即两个最佳观察点之间的采样点。一个在符号判决点附近,另一个在两个符号判决点中间附近,并且与载波相位偏差无关,因此定时调整可先于载波恢复完成,定时恢复环和载波恢复环相互独立,这给解调器的设计和调试带来了方便。

评论