适用于12 bit流水线ADC采样保持电路的设计

随着CMOS技术的迅猛发展,CMOS图像传感器以其高集成度、低功耗、低成本等优点,已广泛用于超微型数码相机、手机等图像采集的领域。而流水线模数转换器以其高速、低功耗、中高精度而被广泛应用于图像传感器的芯片级和列级A/D转换器中。当前,流水线A/D转换器比较成熟的国际水平已达到14 bit 10 MHz。国内已流片成功的大多数是10 bit流水线A/D转换器,因此10 bit以上的高精度流水线A/D转换器还需要进一步研究。在A/D转换器中,采样保持电路作为其前端最关键的模块,它的性能直接决定了整个ADC的性能。

本文采用一种全差分电荷转移型结构的采样保持电路,这种结构可以很好地消除与输入信号无关的电荷注入和时钟馈通;通过底极板采样技术,消除与输入信号相关的电荷注入和时钟馈通;使用栅压自举电路来消除开关的非线性。同时采用折叠式增益增强运算放大器,减小由于有限增益和不完全建立带来的误差。该采样保持电路在5 V电源电压,20 MS/s采样频率下,在输入信号为奈奎斯特频率时,无杂散动态范围(SFDR)为76 dB,采样精度达到0.012%,满足12 bit精度要求。

1采样保持电路

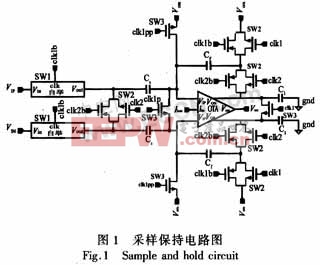

图1为本文设计的采样保持电路结构,该结构称为电荷转移型采样保持电路。

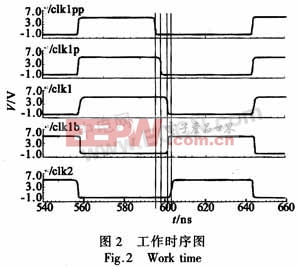

它的工作时序如图2所示,clk1和clk2是两相不交叠时钟,控制采样保持电路分别工作于采样相和保持相;clkb为clkl的反相。当clk1为高电平时,电路进入采样相,运放两个输入端被短路,输入信号存储在采样电容Cs上;clk2为高电平时,电路进入保持相,将差分电荷转移到反馈电容Cf上。

在从采样相向保持相转变的过程中,clklpp,clklp,clkl依次关断,实现了底极板采样,以减少开关时钟馈通和沟道电荷注入的影响;且只有差分电荷转移到反馈电容Cf上,共模电荷一直保存在采样电容Cs上。因此,这种结构可以处理共模范围较大的输入信号。

2采样电容、开关的选取和设计

2.1采样电容的选取

在采样保持电路中,采样电容的取值对电路的性能有直接的影响。采样电容越小,热噪声就大,因为热噪声主要由电路中的开关导通电阻产生,其方差是开关电容值的函数(σ2thermal≈kT/C,其中k为波尔兹曼常量,T为绝对温度),则电路的信噪比(SNR)就降低。如果采样电容较大,会使电路的功耗增大,速度变慢,而此时信噪比主要受量化噪声的限制,没有明显改善。因此在设计时,把噪声限制在一定范围之内,得到电容的最小值,再牺牲一些功耗和速度,取稍大电容值即可。本文所设计的ADC具有12 bit分辨率,量化范围为±1 V。如果要求由热噪声与量化噪声所引起的SNR最多能下降1 dB,即需满足:kT/Cs△2/46.3,△为1 LSB对应的幅度。根据上式算出,采样电容Cs>0.8 pF,取Cs=Cf=1 pF。

DIY机械键盘相关社区:机械键盘DIY

评论