适用于12 bit流水线ADC采样保持电路的设计

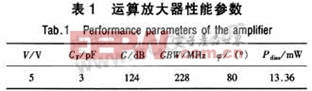

本电路采用CSMC公司的0.5μm CMOS工艺库,应用Spectre对运算放大器和采样保持电路进行仿真验证,表1为典型条件下(TT(工艺角),27℃)运算放大器的性能参数。从表中可以看出,运算放大器的性能满足采样保持电路要求。表中:V为电源电压;CF为负载电容;G为直流增益;GBW为单位增益带宽;为相位裕度;Pdiss抵为功耗。

在采样保持电路的输入端加差分电压1 V,时钟频率为20 MHz,仿真结果表明输出电压达到LSB/2(0.012%)精度内所需要的时间为14 ns,完全满足12 bit的精度要求。

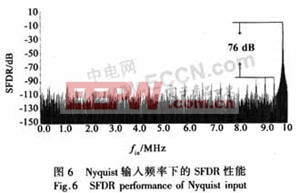

图6是在采样频率为20 MHz下,对由输入信号为Nyquist频率(9.819 3 MHz),Vp-p=2 V的正弦信号,所得到的输出信号频谱图。从图中可以看出电路的SFDR为76 dB,完全满足系统要求。

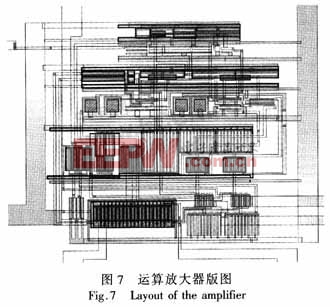

图7为运算放大器的版图,面积为288μm×128 μm(包括主电路、辅助放大器、偏置和共模反馈电路)。该运算放大器作为一个核心模块已流片测试。测试结果表明该放大器性能与仿真值相近,功能正确,可用于该采样保持电路中。

5 结论

本文设计了一个可用于12 bit,20 MS/s流水线ADC中的采样/保持电路。该电路使用CSMC公司的0.5μm CMOS工艺库,在20 MS/s采样频率下,当输入信号的频率为9.8193 MHz时,SFDR为76 dB,精度达0.012%,完全满足12 bit要求。本文运用增益增强型折叠式运算放大器,以获得较高的增益和带宽。同时采用栅压自举开关,并通过对电路中的开关组合优化,极大的提高了电路的线性性能;采用全差分结构、底极板采样来消除电荷注入和时钟馈通。该采样保持电路能够直接应用于高速高精度模/数转换器等各种高速模拟系统中。

DIY机械键盘相关社区:机械键盘DIY

评论