基站电源中同步电路的设计方法

1 引言

本文引用地址:https://www.eepw.com.cn/article/179398.htm在通信电源中,有多路输出的电路常需要将各个输出信号同步,以满足控制的要求。

将电源的各控制芯片同步到系统时钟,也可以减小噪声,改善电源的性能。

另外,在多功率等级的电源中也需要同步,以避免各部分分别开通时产生的离散噪声。各部分同时开通就能同时产生共模噪声,这样就简化了尖峰功率的估算,还能估计到功率分布和损耗的情况,并能根据损耗做母线的电压补偿。

2 同步电路的拓扑形式

芯片可以通过RT/CT端直接连接外部时钟源来同步。芯片内部比较器的高低两个门限决定时间电容CT的充放电过程,当CT开始其充电周期,PWM处于开通的状态,时间电容持续充电直到内部比较器的上限。一旦给出同步信号,放电电路激活,时间电容持续放电直到内部比较器的下限。在放电时PWM比较器无输出,这样PWM处于关断的状态。

外部同步电平的高、低状态可以用数字量1或0来代表。芯片的同步端既可以作为同步信号输入端,也可以作为同步信号输出端。当没有同步端时,时间电路(CT)也可以由数字逻辑(0,5V)工作模式来取代模拟的工作模式。当用数字量来表示电平后,“开通时间”,“关断时间”,“占空比”和“频率”都可以用数字脉冲来表示。如同步信号的逻辑低时间决定了PWM的开通时间,同步信号的逻辑高时间决定了PWM的关断时间。频率,占空比或死区时间可以由PWM时间电容端(CT)的同步信号准确控制。同步信号的高或低可以由555定时器或微处理器来决定。

如果PWM芯片没有连到内部晶振的同步输入、输出端,这时从晶振必须不工作。当从模块使用不同的PWM芯片并具有不同的同步特性如反向的同步信号,这时也必须使从晶振不工作。

但是,这种直接用数字信号同步的工作方法有许多缺点。首先,在电压模式控制时,PWM误差放大器对脉宽没有控制。因为,PWM误差放大器的输出是和一个数字信号相比较,而不是和一个锯齿波信号相比较。从而,通过钳位误差放大器的输出来控制占空比的软启动功能也将无效。这是因为,本身没有时间坡度,电源输出完全由同步脉冲源来控制。只要同步脉冲锁定,PWM输出将根据同步脉冲的电平总是保持完全开或者完全关。当然,没有自身的CT坡度电源将没有自启动,在同步脉冲出现前将总是保持关。电流模式的坡度补偿需要外接其他元器件来实现。每个模块必须设定为主模块或从模块,并且不能随意改变。为了克服这个缺点我们采用一种比较通用的同步方式如图1所示。

图1 同步方式

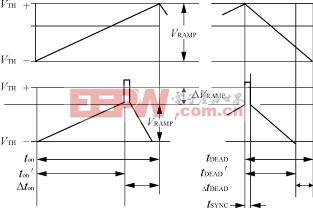

这种同步方法是时间电容CT不直接接地,而是串一个约24Ω的电阻到地,输入同步信号叠加到电阻端电压上(电阻端电压通常为0.5V,这是为了设定一个小的偏置,并且可以影响模块的初始频率),使CT上的电压高于晶振内部门限电压。在同步脉冲出现前,PWM工作在自身的RT,CT设定的频率上。同步信号出现后,同步数字信号叠加到原来的模拟波形上,这种同步方式的RT/CT输入端是模拟和数字信号的叠加,如图2所示。

图2 同步波形

工作时,同步脉冲使CT上的电压迅速高于PWM比较器的上限,晶振的充电状况迅速翻转,晶振开始与同步信号同步的放电周期。

图1所示方法具有如下优点:可以从任何的PWM芯片取得同步信号或者同步任何PWM芯片,且芯片的数量不限,双向的同步信号,对于简单的系统可以用数字信号同步,CT上的坡度可以做斜坡补偿,每个模块没有严格的频率设定,而且可以远端关断。

增加同步电路将对PWM的占空比,死区时间和坡度产生较小的影响。

3 同步电路参数计算

首先,我们必须选定晶振的时间部分参数以保证同步。同步时锯齿波的幅度要比电压上限低,否则,在同步脉冲来之前比较器就动作了,这将使同步脉冲失效。为了可靠工作,应该使PWM晶振的工作频率比同步频率低。通常低10%。如图3所示。

图3 同步时间参数

DIY机械键盘相关社区:机械键盘DIY

评论