500兆/秒高速A/D系统的实现

摘要:介绍采样率为500兆/秒、采样精度为8bit的高速A/D系统的设计结构以及高速电路设计中的问题,最后还讨论了如何在Windows95下设计具有实时性要求的程序。

本文引用地址:https://www.eepw.com.cn/article/179084.htm关键词:高速A/D变换 高速电路设计 Windows95 实时程序设计

在现代雷达系统、激光测距以及高能物理试验中往往产生宽带信号或者上升沿比较陡的信号(一般10ns左右)。若对此类信号进行数字化处理,要求A/D部分的采样率至少应该在200M/s以上。本文介绍的系统正是针对这样的要求而开发出来的。

1 系统结构

系统分为A/D转换和数据传输控制两大部分(图1)。数据传输控制部分作成PC机的插卡在计算机的PCI扩展插槽内,它的主要功能是将A/D采样得到的数据传递给计算机,同时产生相关的控制信号去控制整个系统;A/D转换部分由于受到电源和体积的影响单独作成一个模块置于计算机外部,其中关键的核心器件ADC采用的是MAXIM公司推出的MAX101A,它的最高采样率可达500兆/秒,采样精度为8bit。两部分之间的数据传递通过扁平电缆来完成。

2 A/D转换

2.1信号调理

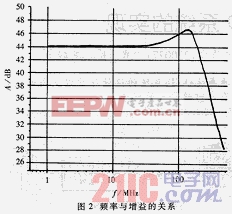

对于高速A/D采样电路来讲,前端调理电路显得尤为重要,不仅要有足够的带宽,而且还要将单端的输入信号变成差分信号提供给ADC,以减少偶次谐波的产生,同时本身的噪声也要很小,这样才不会对ADC的精度产生影响。考虑到上述因素,在前端部分采用了AD公司的AD8138作为缓冲放大器,它的性能指标为:-3dB带宽320MHz,输入噪声5nV/(根号Hz)。AD8138为表面封装器件,本身的体积非常小巧,使得ADC与信号输入点的距离可以很近,大大减少了外界噪声的影响。经测试,器件的模拟带宽为230MHz(图2)。

评论