基于Cadence_Allegro的高速PCB设计信号完整性分析与仿真

2.3 对AD数据信号的仿真分析

对ADC通道A第0位的SI仿真如图5所示。本文引用地址:https://www.eepw.com.cn/article/178953.htm

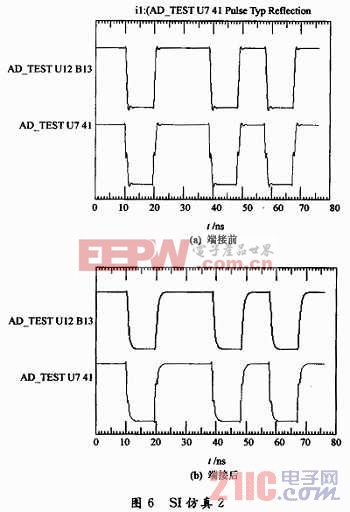

如图6所示,采用端接电阻后数据波形质量明显提升,端接能有效解决阻抗不匹配所引起的反射问题。

3 结语

Cadence_Allegro软件中的Specctraquest和Sigxp组件工具,为高速PCB的设计与仿真提供了强有力的支撑,包括仿真模型验证、拓扑分析、布线前与布线后仿真、约束条件的设置、PCB布局布线等硬件环节,通过仿真结果可促使设计者较好地把握信号完整性问题,优化设计,提高高速PCB设计的一次成功率,较好地应对高速设计所面临的挑战。

评论