串行A/D与FPGA在微型数据记录仪中的应用

摘要:以ADS8341为例,介绍了基于FPGA使用串行输出A/D转换器实现对多通道准同步采样的方法,逻辑控制方式FPGA相比程序流程式的单片机而言,运行更为可靠,通过时序仿真和试验验证了该控制方法的正确性,系统体积小、集成度高,适用于容积小、功耗低的场合。

关键词:AD8341;同步采样;FPGA

0 引言

在现代电子技术应用领域,A/D转换器是模拟信号转换数字信号的中介,数据采集系统中,一般由单片机或其他微控制器对高精度A/D转换器进行控制,通常采用软件模拟A/D转换器时序的方法,增加了CPU的负担,降低了CPU的工作效率,现场可编程门阵列FPGA(Field Programmable GateArray)的高集成度和高速特性,使之相对于单片机和微控制器更适合用于高速A/D器件的采样控制。另外,在电磁干扰较大的环境中,单片机会出现程序跑飞的问题,在利用看门狗复位的过程中,对采集的数据流而言,会存在数据的丢失问题。相对的,触发沿或电平控制的FPGA,通过设计可靠的驱动,系统采集数据更为可靠。

本文是以一个3通道低频小型数据记录仪为研究背景,设计了以Actel公司FPGA为控制器的系统,对串行输出A/D转换器ADS8341进行控制,提高了系统集成度和稳定性。

1 ADS8341功能介绍

ADS8341是Burr Brown公司推出的一款低功耗,高性能的4通道,16位A/D转换器,其串行接口降低了系统开发的成本,SSOP-16的小体积封装适合微型设备使用。

1.1 ADS8341的功能

CH0~CH3:4个通道为模拟输入端,可以设置为单通道输入方式,也可以构成CH0-CH1,CH2-CH3,两组差分输入。

![]() :引脚低电平有效,A/D转换器进入低功耗模式。

:引脚低电平有效,A/D转换器进入低功耗模式。

Vref:参考电压输入端。

DCLK:系统的外部时钟输入端,最高输入为2.4 MHz,此时芯片A/D转换速度达到最大值,为100 ksa/s。

![]() :A/D转换器的片选端,低电平有效,高电平时其他引脚呈高阻态。

:A/D转换器的片选端,低电平有效,高电平时其他引脚呈高阻态。

DIN:串行数据输入端,片选信号有效时,在DCLK的上升沿,串行数据按位输入A/D。

DOUT:串行数据输出端,片选信号有效时,在DCLK的下降沿,将A/D转换后的数字信号按位输出。

BUSY:片选有效时,A/D转换器输出一个时钟周期高电平信号。

Vcc和GND引脚分别为电源和数字接地端。

1.2 ADS8341的控制宇及转换时序

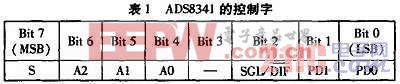

ADS8341的控制字如表1所示:

ADS8341的控制字为8位,S为起始标志位,A2,A1,A0控制通道选择,可以提供单通道或差分输入方式不同通道选择。*****高电平为单通道输入方式,PD1,PD0为电源控制模式位,若为“11”,电源始终处于开启模式。

评论