节省基站功耗的低压差(0V)稳压器

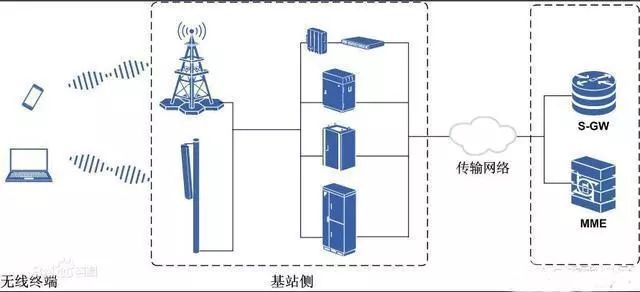

电信基站等设备需要多路供电电源,以满足不同的输出电压、输出电流要求。机房的主电源通常先被转换为+48V或-48V直流电源,然后根据需要传送到各个系统设备,最后再转换成较低等级的电源电压。

本文引用地址:https://www.eepw.com.cn/article/177901.htm常见的设计方案是利用电源模块或现成的转换器(砖)将48VDC(或-48VDC)电源转换到一个较低的电源电压,然后再由电源模块或PCB板上电路将其转换为要求的各种电压。一个典型例子是,从48V输入转换到8.5V,通常这个8.5V与48V输入是电气隔离的。

将8.5V电源分别转换成用于RF功率放大器的7.5V(基站设备)和用于逻辑电路的5V、3.3/3V,或用于FPGA、处理器核的1.8V电压。考虑到系统所要求的供电电流和功耗指标,采用开关模式降压转换技术从8.5V产生较低的电源,而对于RF级的7.5V电源则大多采用 低压差线性稳压器(LDO)实现,以满足射频电路的低噪声要求。

线性稳压器会根据输出电压的要求调整输入与输出的压差,因而要消耗一定的功率(电流与输入/输出压差的乘积),表现为调整管的热耗。为了提高散热能力,设计人员不得不折中考虑输入/输出压差、功率耗散、调整管选择等因素,以便在规定的负载电流和输入电压范围内可靠地工作在线性区(非饱和、截止)。在本文介绍的电路中,输入电源电压随着系统负载的变化量可能达到100mV,压差可能达到900mV,由此可见,8.5V的电源电压刚好满足要求。本例中标称压差1V刚好能够接受。

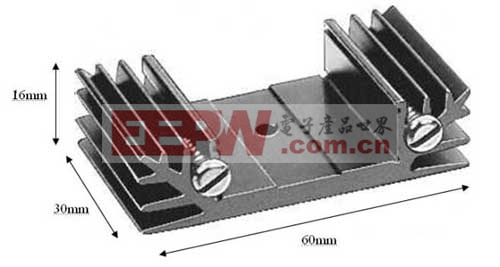

多数所谓的LDO其实际压差会高于1V,因此这些器件需要输入与输出之间保持更大的压差裕量。对于1V压差,调整管上的功耗为1V×10A=10W。如此大的功耗要求系统提供合理的热管理方案,并因此会增加小型散热器及相关材料成本和装配时间。如图1所示,采用6.8ºC/W典型系数的散热器(比如Aavid Thermalloy公司的散热器)和TO-220封装的的温升将高出室温68ºC左右(为简化起见,忽略RθJC降额系数及其它热阻的影响)。考虑到机架内部其它功率元件,其内部温度通常要高于外部环境温度,散热片甚至可能工作在100ºC以上。为了保证系统可靠工作,这种情况下显然无法使用更小的散热片。

图1:典型的6.8ºC/W散热器。

设计中需要低RDS 场效应管(FET),以降低串联调整管的压降,从极性考虑要求使用P沟道器件。而具有相同架构的P沟道FET其导通电阻可能是N沟道FET导通电阻的两倍以上,另外,P沟道FET的价格也比较高。

为便于比较,我们可以考察一下国际整流器公司(IR)的P沟道管IRF9Z34N和N沟道管IRFZ34,二者的击穿电压均为55V。100ºC时,P沟道器件的导通电阻为100mΩ,可承载12A电流;而N沟道器件的导通电阻仅为40mΩ,可承载电流为18A。P沟道器件的价格大约贵两倍。

提供10A峰值电流时,P沟道FET的导通压降是1V,而具有40mΩ RDSon的N沟道FET的导通压降为400mV。另一种选择是使用 PNP晶体管,但即使是这样,集电极与发射极之间的饱和压降也会达到200mV。还可以选择性能超过双极性技术的超低RDSon N沟道FET,但这种器件需要更高的栅极驱动电压。如果能够找到驱动超低RDSon N沟道FET的方法的话,上述问题将迎刃而解。

这也正是开关模式转换器所面临的一个设计挑战,为了驱动超低RDSon N沟道FET,可以采用电压自举技术:将一个动态开关电压通过二极管进行交流耦合,再对储能电容充电,就可得到高于输出电压的N沟道FET栅极驱动电压。如果电路板或电源模块内含有降压转换器,则可利用其开关信号产生线性稳压器所需的栅极驱动电压。

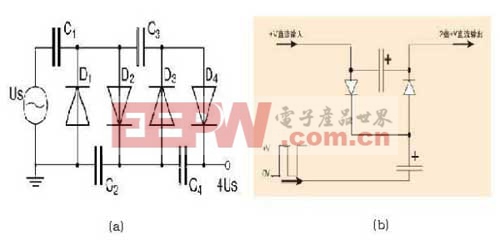

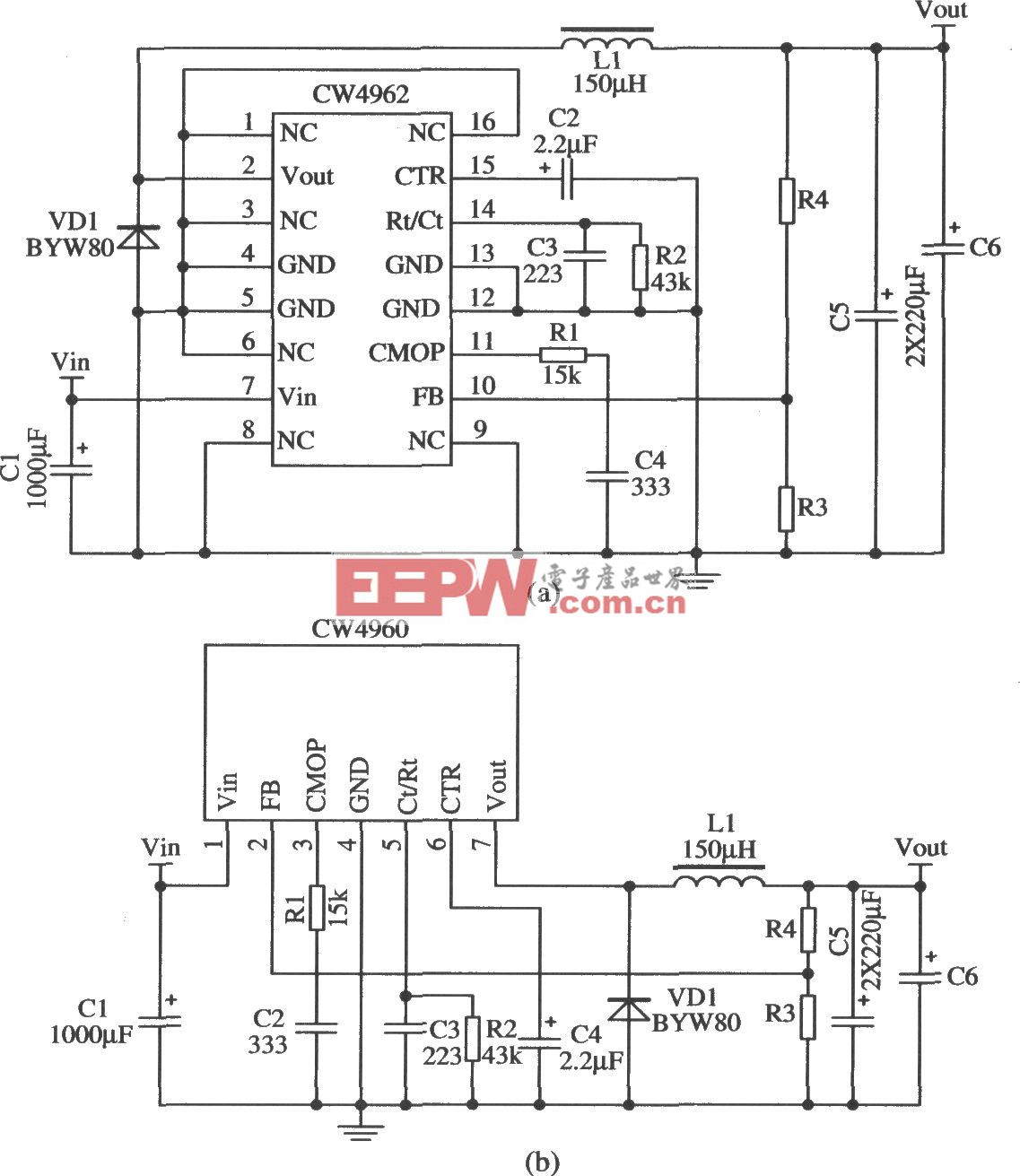

也就是说,我们可以将降压转换器的开关节点连接到简单的倍压电路。常见的倍压电路是半波系列乘法器,也称作维拉德(Villard)级联电路(图2)。幅度为±Us的交流电压作用到该电路可以获得4倍的输出,即输出端得到4Us。

开关电压相对于地电平的摆幅为Us时,该电路可产生4Us的输出,而降压转换器开关节点的摆幅大约为Vin至地电平。因此如果降压转换器的供电电压为8.5V,则其进入电感的开关电压为0V至+8.5V,得出Us=4.25V,如图2所示。

图2:(a) Villard级联倍压电路;(b) 倍压电路输入为+V,开关幅度为+V,产生2倍(+V)输出。

如果考虑转换器的占空比,则需作进一步的复杂计算,因为占空比与输入、输出电压比和负载有关,为便于讨论,我们假设占空比为50%,可以利用图2电路获得大约17V的电压。需要输出更高电压时,可以级联更多的倍压单元电路,一级倍压使用两个二极管和两个电容,可产生低电流直流输出(图2a)。

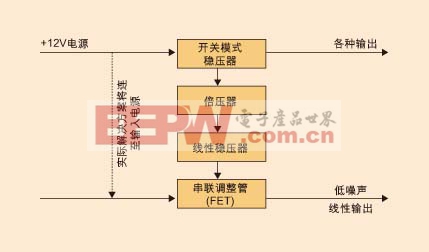

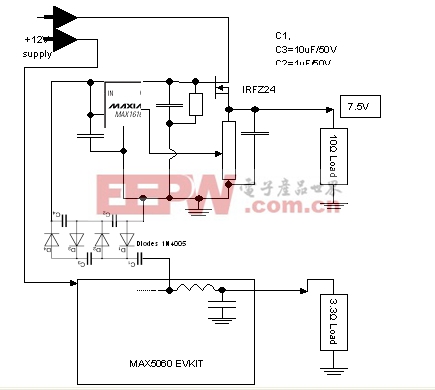

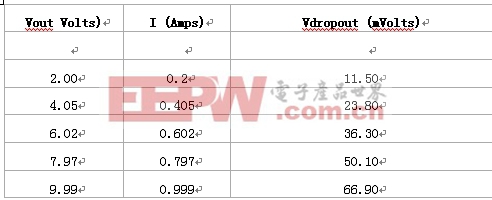

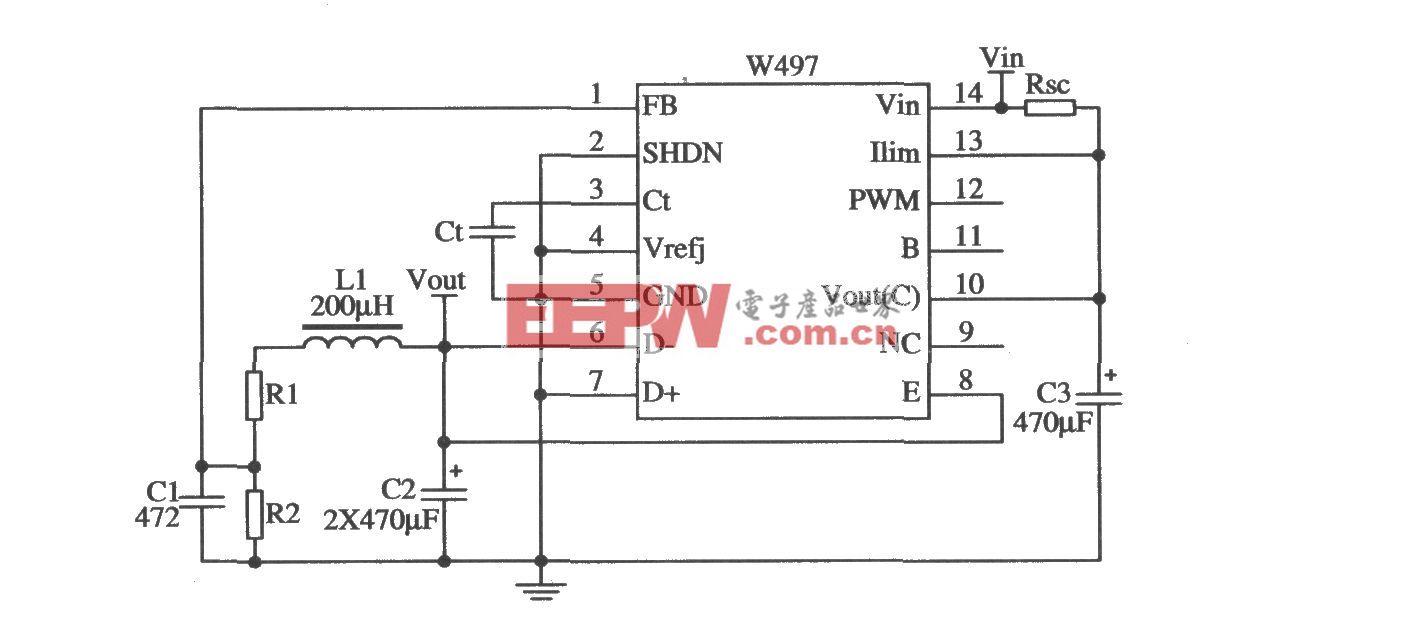

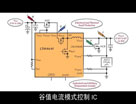

我们可以将上述电路产生的17V DC应用到一个简单的低电流线性稳压器(如MAX1616),目的是为低RDSon N沟道FET提供栅极驱动。FET器件采用8.5V供电,输出7.5V为RF放大器供电,通过电位器分压反馈网络调节线性稳压器输出。该电路利用MAX5060评估板、MAX1616线性稳压器、N沟道功率MOSFET以及相关的其它元件进行了测试,简化原理图如图3所示,实际电路如图4所示。

图3:零压差稳压电路框图。

电路工作原理

MAX5060EVKIT降压转换器可产生3.3V电压,输出电流达20A,开关频率约为270kHz,由12V输入产生3.3V输出。由于图4电路工作在轻载条件下,负载电流只有1A,作用在电感上的电压波形占空比为25%,摆幅介于地电平和12V之间。利用该开关电压驱动倍压电路,可以在线性稳压器(MAX1616)的输入端得到大约24V的直流电压。实际倍压输出为22.7V,能够为线性稳压器提供足够的驱动。线性稳压器的输出可驱动低RDSon N沟道FET(IRFZ24N)的栅极。

利用一个可调电源为场效应管供电,从而允许根据输入、输出电压的范围调节压降。FET的栅极由MAX1616 LDO的22V输出驱动,并在分压网络R1的电压达到1.24V之前始终将场效应管驱动在导通状态,随后关闭FET驱动器,使稳压器保持平衡。

电阻R2和电容C2通过抑制高速瞬态响应和噪声来控制环路的动态特性。电阻R2还可作为线性稳压器的自身负载吸收FET关闭时的电流。通过选择分压网络的电阻比设置输出电压值。在该应用中,R1选用250kΩ电位器,因此能让MAX1616的输出摆幅从1.25V上升到22V以上。

在不同输入电压、负载下观察FET栅极驱动电压的跌落测量压差,由此确定电路进入闭环控制的工作点。一旦栅极驱动跌落到MAX1616 LDO所能提供的22V以下,电路将进入稳压调整状态。测量调整管两端的输入、输出电压之差,可以确定电源电压、负载变化范围内的压降。

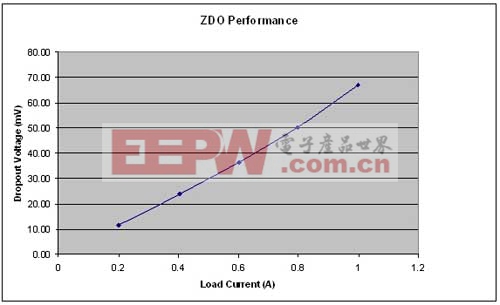

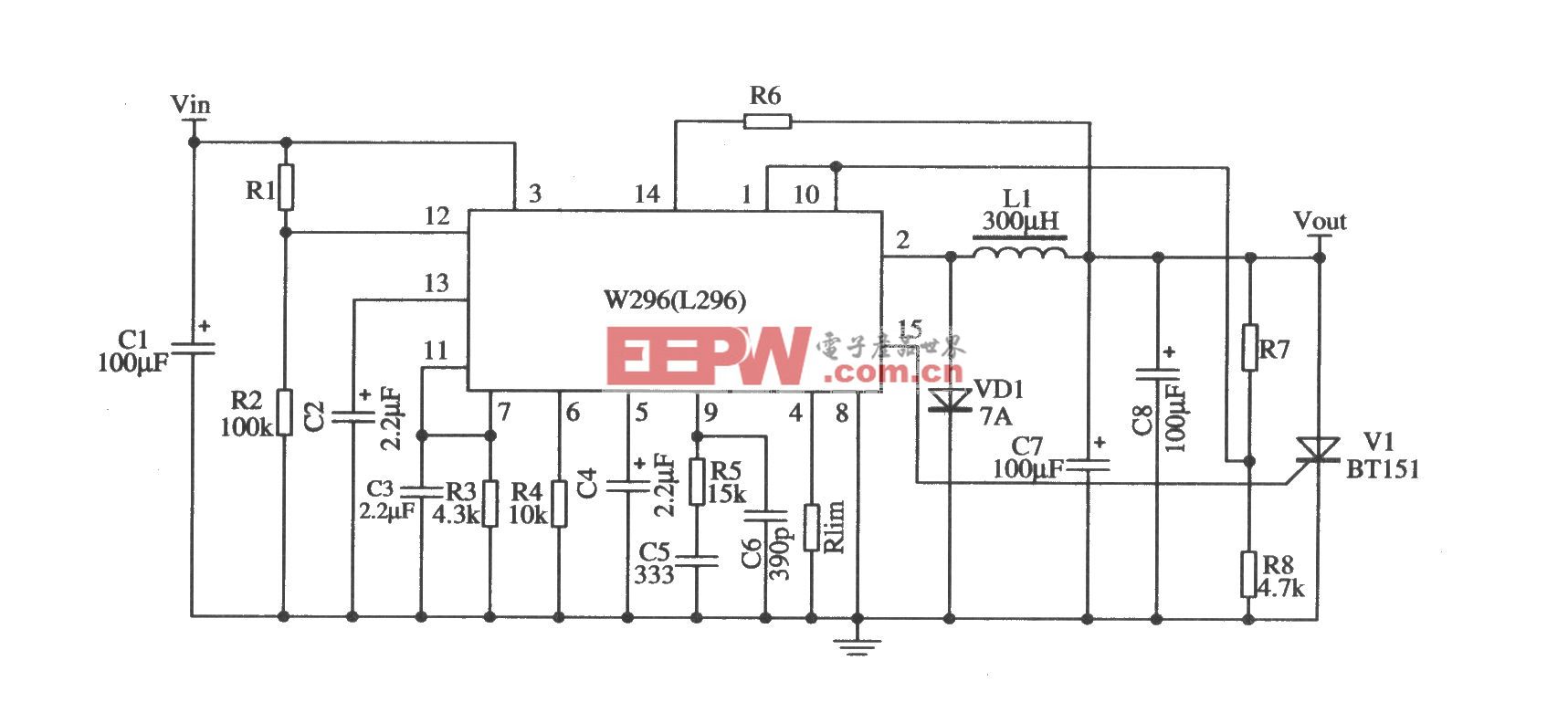

这种方法已经被证明是确定线性调整管压降的行之有效的途径,它从侧面反映了MOSFET的RDSon,图5以表格和图形的方式给出了对该电路的性能测试结果。

本文小结

图4所示电路提供了一个零压差稳压器(ZDO),可利用N沟道、低RDSon FET实现,MOSFET的栅极通过倍压电路驱动。降低输出负载会减小输入、输出之间的压差,空载时达到零。大电流应用中,该电路能够降低稳压过程中的调整管损耗,进而降低对散热器及其他热管理技术的要求。

图4:零压差(ZDO)电路原理图。

基站系统的LDO要求1V的压差裕量,采用ZDO可大大降低这一裕量,对于需要10A输出电流的应用,可以选择具有极低RDSon的场效应管IRF1324,其RDSon低于1mΩ,利用该FET构建的ZDO理想情况下的压差为每安培1mV。

在本文提供的例子中,所使用的FET即使在最糟糕的工作条件下也能有效降低调整管的功耗,考虑到负载变化及其他因素的影响,只需100mV的压差裕量,再加上FET RDSon需要的10mV压差,可以将原来的8.5V中间电压降至7.61V。总压差为110mV,10A电流对应的功耗为1.1W,节省大约9W的功率。利用表面贴装器件可直接通过PCB的覆铜区域散热,因此可以很容易解决热管理问题。总之,使用IRF1324可省去散热器,降低成本,简化安装过程,并为系统节省9W的能耗。

图5:图4所示ZDO电路的测试结果。

ZDO还可用于电池供电系统,系统所能提供的压差裕量会随着电池的工作电压而发生显著变化,ZDO在这样的系统可有效延长电池的工作时间。

表1:零压差稳压器电路的主要性能。

备注

本电路只是原理电路,只在直流轻载下进行过测试。读者可以对其作进一步的开发,以优化动态负载响应及低输入/输出压差特性。

评论