动态扫描数字钟电路设计与制作

0 引言

本文引用地址:https://www.eepw.com.cn/article/174976.htm在电子技术实验教学中,构建的电路设计理念,提高的电路设计能力,是教学的根本目的和核心内容.数字钟电路的设计包括了时序逻辑电路.组合逻辑电路.数码管显示电路和脉冲信号产生电路等内容,内容涉及面宽.综合性强,是电子技术自主性实验教学的典型案例.文中采用了石英晶体振荡器电路.计数电路.动态扫描及译码驱动电路.显示电路和时钟校正电路,来实现该电路.

1 系统设计方案

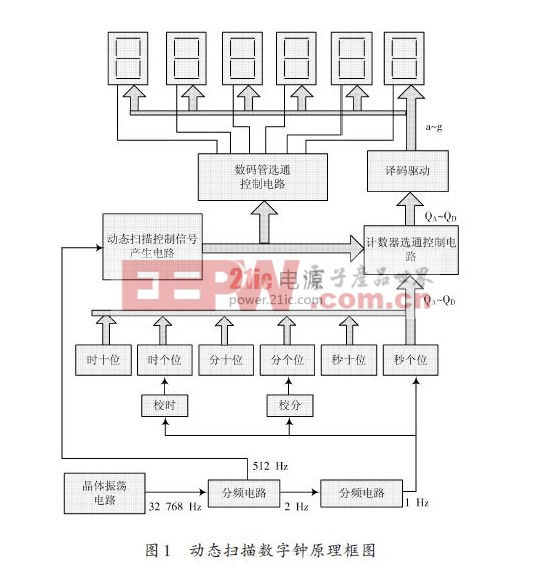

本次设计的数字钟,实现对时.分.秒的数字显示,周期为24 h,显示满刻度为23 时59 分59 秒,并具有校时功能.电路主要采用中规模CMOS集成电路,采用电池作电源,通过共阴极LED 数码管显示时钟.该系统由秒脉冲产生模块.计数器模块.译码显示电路模块.动态扫描模块.校时模块组成.其中秒脉冲产生模块由晶体振荡器电路和两个分频器电路组成,动态扫描模块由动态扫描控制信号产生电路.计数器选通控制电路和数码管选通控制电路三部分组成,系统组成框图如图1所示.

1.1 秒脉冲产生电路

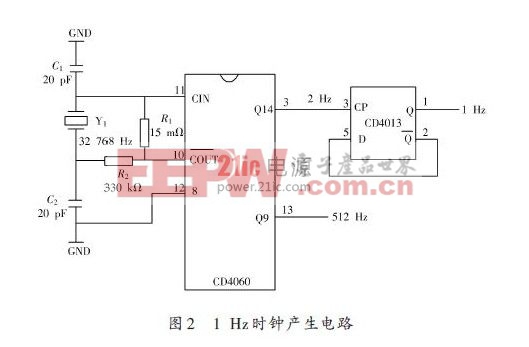

秒脉冲信号由石英晶体振荡器产生,由于晶体振荡器输出频率较高,为了得到1 Hz 的秒信号,需要对振荡器的输出信号进行分频.通常的分频器采用多级二进制计数器来实现.将32 768 Hz 的高频方波信号经32 768(215)次分频后得到1 Hz的方波信号供秒计数器进行计数,即实现该分频功能的计数器相当于15 级二进制计数器.

本次设计采用CD4060 来构成14 级2 分频电路.

CD4060的9脚.10脚.11脚内含两个非门电路,1脚输出12分频信号,2脚输出13分频信号,3脚输出14分频信号.利用CD4060的两个非门和32768Hz的晶振构成32 768 Hz 的振荡器,然后通过CD4060 进行214 分频得到2 Hz的信号,再经过D触发器CD4013进行一次二分频即可得到1 Hz的秒脉冲.电路图如图2所示.

1.2 计数器设计

计数器电路用来完成60 秒60 分及24 小时的计数工作,且秒计数器的进位脉冲作为分计数器的输入脉冲,同理分计数器的进位脉冲作为小时计数器的输入脉冲.“ 秒”.“ 分”.“ 时”计数器电路采用同步加计数器CD4518来完成.

(1)CD4518双BCD同步加计数器

CD4518 是一只双BCD 十进制计数器,它含有2 个独立的计数单元,有2个计数脉冲输入端,上升沿触发端CP 和下降沿触发端EN,若用CP 来触发,则EN 接高电平,且为上升沿触发;若用EN 来触发,则CP 接低电平,且为下降沿触发;有4个输出端QD~QA,一个清零端.

CD4511的引脚图如图3所示.其中:

CP:时钟输入端,上升沿触发;

EN:时钟输入端,下降沿触发;

R:复位端,高电平时计数器=0;

QD~QA:计数值十进制输出端;

UDD:正电源输入端(3~15 V);

USS:电源参考地.

分频器相关文章:分频器原理 尘埃粒子计数器相关文章:尘埃粒子计数器原理 三维扫描仪相关文章:三维扫描仪原理

评论