AD1672模数转换器的工作原理及其应用

一、 概述

本文引用地址:https://www.eepw.com.cn/article/172370.htmAD1672是美国adi公司最近推向市场的一种新型单片式模数转换器(ADC)。片上含有4个高性能采样保持放大器(sha)和4个闪烁式adc及电压基准。它采用4级流水线结构,输出带有误差修正逻辑电路,并采用bicmos工艺,从而保证在3msps采样速度下12位精度,在整个工作温度范围内不失码。由于ad1672输入sha具有快速建立特性,所以它既适合从负满度到正满度电压逐次切换多通道系统,又适合输入频率高达奈奎斯特速率的单通道采样。

ad1672具有宽频带输入、单电源供电、低功耗和低价格等特点,非常适用于通信、图象处理和医疗设备新电路设计。 ad1672采用28脚plcc封装,工作温度范围为-40~+85°c,其引脚排列见图1,引脚功能说明见表1。

图1 ad1672引脚排列

类型:ai—模拟输入;di—数字输入;p—电源; ao—模拟输出;do—数字输出。

表1 ad1672引脚功能说明

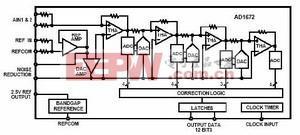

ad1672采用4级流水线闪烁式(flash),又称并行式模数转换结构(见图2)。

图2 ad1672 结构框图

4级闪烁式adc的分辨率分别为4,4,3和4位,其中每两级之间重叠1位用来误差修正。用低噪声sha采集满度值,单端输入在167ns内具有12位精度。ad1672的工作过程,首先第一级闪烁式adc对输入信号进行4位近似转换,同时利用第1级数模转换器(DAC)将这4位数字量转换成对应的精确模拟量。再从第1级sha输出的模拟量减去第1级dac产生的模拟量得到一个残差。然后,第2级sha对这个残差进行采样和保持,第2级adc对此进行4位近似转换,同样利用第2个dac得到第2级残差。一但第2级sha进入保持方式,第1级sha便返回到采样方式,以采集新的输入信号。第3级转换与第1级和第2级类似,也由一个sha,一个adc和一个dac构成,不同之处分辨率不是4位而是3位。第4级,即最后一级转换仅由1个4位闪烁式adc构成,完成最终残差的模数转换。最后在修正逻辑单元,累计4级闪烁式adc构成15位输出,但由于在累计过程中采用了适当的误差修正方法,使最终输出字为12位。数字输出连同超量程指示(otr)都被锁存到输出缓冲器以驱动输出引脚。

由于ad1672结构的每一级都有一个附加的sha,所以允许流水线转换。实际上这种模数转换器是由多级输入,同时转换,通过串行链方式完成四级转换过程。这表明,虽然这种转换器在每个时钟周期都具有捕获新输入信号的能力,但要完成全部转换并且在输出端呈现数字量,实际上只用2 1/2个时钟周期。这种“流水线延迟(pipeline delay)”在许多应用中它并不引人注意,只是在有些情况下才考虑这个问题。例如,在高速反馈环路要求使用adc的一些场合,只有提供一个理想的数字输出结果,才能对其输入信号进行补偿(例如,视频应用中的失调校准或零点恢复)。在这种情况下,在计算环路稳定性时,必须考虑通过流水线引起的时钟延时。另外,由于转换器同时在3个转换器上工作,所以在转换过程的主要交接处(例如,电源或基准引起的大的尖峰毛刺)会使3个采样数据变坏。最后应当说明,ad1672存在一个最小的时钟速率,低于这个最小值,sha的顶降率会使流水线信号变坏,这个最小时钟速率在25°c 时为20khz。通常时钟速率选取3mhz。

ad1672的内部定时控制电路利用了时钟的上升沿和下降沿。ad1672在时钟输入的上升沿对模拟输入信号采样。当时钟处于低电平期间(处于时钟下降沿和上升沿之间),输入sha处于采样方式;当时钟处于高电平期间,则sha处于保持方式。由于这种器件利用时钟上升沿和下降沿定时,所以仅在时钟上升沿,抖动才很明显。

三、应用

1.模拟输入

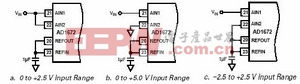

ad1672等效模拟输入电路如图3所示,其中输入sha及其辅助电阻网络很容易接成单极性(0~2.5v或0~5.0v)或双极性(-2.5~+2.5v),见图4。ad1672标称输入电阻rin,对于 2.5 v输入范围为2kω,对于5.0v输入范围为4kω。

图3 等效模拟输入电路

图4 输入范围选择

评论