基于Nios的GDM12864A显示模块控制

随着微电子技术的迅猛发展,各种芯片在体积不断缩小的同时,功能却越来越强大。FPGA芯片也从最初只有几千门,发展到数百万门的规模,I/O口由几十个发展至上千个。在这种资源极其丰富的情况下,FPGA设计者不再满足于仅仅用其来设计简单的应用系统,而开始在一片FPGA上集成一个完整的电子系统,即SOPC(System On Progratomble Chip)。它通常包括片内存储器和片内微处理器。Altera公司针对其FPGA芯片推出的Nios系列处理器,就是专为SOPC设计而开发的,它是Altera Excalibur嵌入处理器计划中第一个产品,它成为业界第一款可编程优化的可配置处理器。本文阐述在SOPC中利用Nios处理器实现GDM12864A显示模块控制的方法。

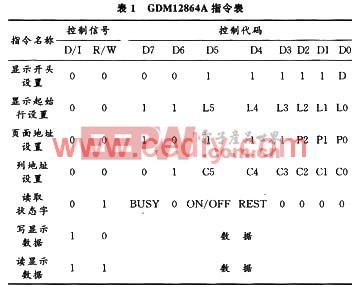

本文引用地址:https://www.eepw.com.cn/article/169483.htmGDM12864A是带显示存储器的图形液晶显示控制器。它的特点是内置64×64 b的显示存储器,显示屏上各像素点的显示状态与显示存储器的各位数据一一对应,显示存储器的数据直接作为图形显示的驱动信号。显示数据为“1”,相应的像素点显示;显示数据为“0”,相应的像素点就不显示。同时GDM12864A配备了一套显示存储器的管理电路和与计算机接口电路,允许计算机直接访问显示存储器。其具体参数如下:64×64 b(512 B)的显示存储器,其数据直接作为显示驱动信号,8位并行数据接口,64路列驱动输出,低功耗,在显示期间功耗最大为2 mW,较宽的工作电压,Vcc=2.7~5.5 V,Vee=0~-10 V。GDM12864A详细指令如表1所示。

2 Nios软核

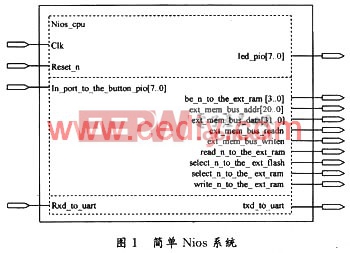

Nios处理器是Altera公司推出的一个具有32/16 b精简指令集的软核(Soft Core)CPU,它是面向用户,可以灵活定制的通用RISC嵌入式处理器,它以软核的形式交付给用户,并针对Altera公司的FPGA专门进行了优化。用户可以在Altera公司提供的开发软件中加载Nios核和相应的外围接口并定义相应的指令,然后对设计进行综合并下载到FPGA中就可以方便地定制一个具有特定功能的嵌入式处理器。用户可以按照设计的需要选择添加必要的部件,不会出现资源浪费的现象。图1即为一个已经设计完成的基本的Nios系统,它包括了一个嵌入式系统工作所需要的所有基本端口,其中有ROM和RAM接口,串口,UART,以及系统的时钟Clk,另外还有一些外设接口。

3 Nios与显示模块的接口电路

利用Nios对GDM12864A进行控制可以有两种方法:一种方法是将该显示模块的接口作为Nios的存储器或I/O设备直接挂接到Nios的Avalon总线上,Nios以访问I/O设备或读写存储器的方式对其进行控制。另一种方法是将GDM12864A的接口与Nios的并行端口相连接,Nios通过对其端口的操作来完成对显示模块的控制。这种方式具有时序简单,易实现的优点,可以直接利用软件完成所有的控制操作。本文将采用第二种控制方式,其接口电路如图2所示。

图2中DI为寄存器选择信号,高电平时选择数据寄存器,低电平时选择指令寄存器;RW是读写控制信号,RW为高电平时Nios可以从显示模块读取当前状态,为低电平时Nios向显示模块写数据或指令;E为使能信号。由于GDM12864A是128×64像素的显示屏,显示时被分成两个区域分别显示,所以在进行控制时需要进行显示区选择,也就是片选CS1和CS2。DB[7..0]为并行数据接口,发送指令或读取状态都通过对它的操作完成。

评论