基于NiosⅡ的VGA彩条信号显示的实现

摘 要:VGA 作为一种标准的显示接口得到广泛的应用。依据VGA 显示的原理,提出了一种基于Nios Ⅱ处理器的VGA 时序彩条信号显示的实现方法。利用FPGA 产生VGA 时序信号,Nios Ⅱ处理器控制输出彩条的颜色,按键控制彩条的输出模式,将要显示信号的数据直接送到显示器,这样就加快了数据处理速度,节约了硬件成本。

本文引用地址:https://www.eepw.com.cn/article/168337.htm关键词: FPGA ;Nios Ⅱ;VGA ;彩条信号

1 引 言

Altera 开发了整套工具(包括SOPC Builder ,Nios Ⅱ集成设计环境和Quartus Ⅱ开发软件) 帮助用户加速硬件和软件的开发,实现完整的基于可编程逻辑的SOPC 解决方案。SOPC Builder 是在Altera FPGA 中实施IP 的关键工具。该系统级工具使用Altera 的MegaWizard 技术自动生成AvalON 的交换架构,将设计中的不同功能模块连接在一起。SOPC Builder 还会生成定制软件开发工具,根据需要为由Nios Ⅱ处理器控制的功能模块提供合适的软件头文件。Nios Ⅱ IDE 是Nios Ⅱ软核处理器的主要开发工具。他为软件开发提供了一个集成的设计开发环境,包括一个具有工程管理、源代码开发、基于J TAG 调试功能的图形用户界面( GUI) ,大大简化了大量复杂的NiosⅡ处理器设计。业内领先的Quartus Ⅱ软件为硬件开发提供了设计采集、综合、仿真和布局布线功能。Quartus Ⅱ软件是最具成本效益的FPGA 开发套件。

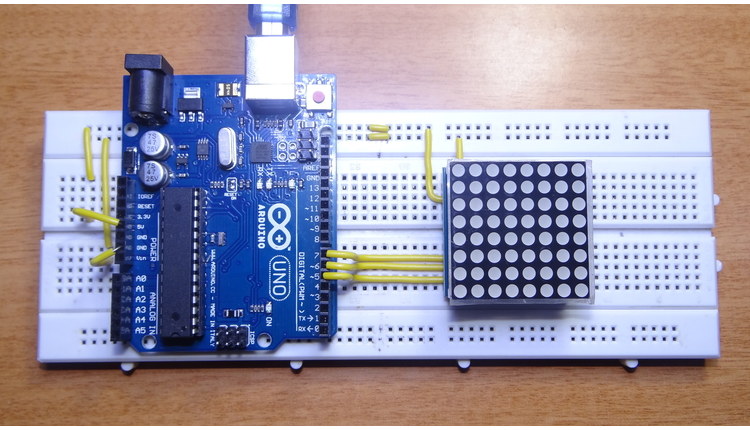

本VGA 输出显示实例采用Altera DE2 嵌入式系统开发板,实现了嵌入式VGA 彩条输出显示。

2 VGA 信号时序

评论