基于SATAII协议的CRC32并行算法的研究

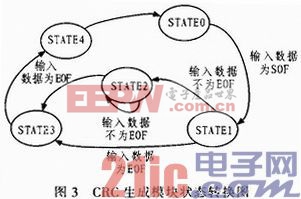

SATA协议中CRC生成校验模块采用有限状态机来识别传输数据流中的原语,从而完成CRC值的生成与校验。其状态机结构图如图3所示。本文引用地址:http://www.eepw.com.cn/article/159619.htm

其中状态STATE0检测帧头并装入STATE1状态;在STATE1中,当输入数据为帧尾时,则转入STATE3状态,否则转入STATE2状态,在STATE1状态下输出帧头,并设置CRC初始值为0x52325032h;在STATE2中,当输入为帧尾时,则转入STATE3状态,否则转入STATE2状态,对非原语数据进行CRC值生成,并保存到寄存器中,输出为数据或保持原语;在STATE3中输出最终的CRC值,并转入STATE4状态;在STATE4中输出帧尾,并转入STATTE0状态等待下一次数据的输入。

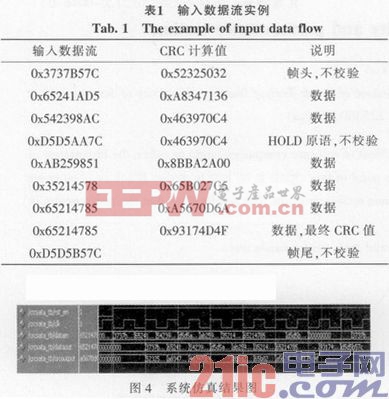

输入一帧数据,并由式(14)进行计算,得出输入数据对应的CRC计算值如表1所示。

其对应的系统仿真结果如图4所示。

仿真结果显示,CRC数据校验与表1中的理论值一致,CRC生成模块能够自动识别数据流中的原语和数据,并能有数据生成正确的CRC校验值。其中每双字数据生成CRC值仅需一个时钟周期,系统输出延时仅为一个时钟周期,相对于串行CRC生成算法,CRC32并行算法更能满足SATA协议对时钟频率的要求。

5 结束语

文中介绍了CRC校验原理和常用CRC32实现算法,并根据比特型算法推导出一种CRC32并行算法的实现方案,该方案实现简单,实现的并行算法相对于串行算法具有速度快,运算简单,并且易于硬件实现等优点。本文还将将CRC32并行算法与SATA协议相结合,实现了满足SATA协议规范的CRC生成和校验模块,并成功应用于SATAⅡ主控制器的设计中。

评论