基于SATAII协议的CRC32并行算法的研究

串行比特型算法可以很容易通过带反馈的移位寄存器的硬件实现,其吞吐率可以达到200 Mbps,但是远远不能达到高速通信系统的要求。

对于查表法生成CRC校验码,要预先汁算好所要的有效信息位,并存放信息位表中,然后按信息位的顺序计算好所有校验位,并存放于表中,待要使用时通过查表输出对于的CRC校验值。但这种方法需要较大的存储空间存储长度较大的CRC余数表,并且随着并行位数的增加,余数表的长度按指数增加,对于CRC32规范也不具有现实性。

因此,SATA协议中需采用并行CRC32算法以达到3 Gbps的吞吐率。

3 CRC32并行算法推导

CRC32并行算法可由串行比特型算法推导而出。

令需进行校验的32位数据以Q0表示,32位移位寄存器初始值用M0表示即:

Q0=[D0D1D2D3…D31]T (8)

M0=[C0C1C2C3…C31]T (9)

自反馈的移位运算可以采用状态转移矩阵表示,i+1次移位后寄存器的状态Qi+1与i次移位后寄存器的状态Qi之间的关系可通过状态矩阵A表示为:Qi+1=AQi,进一步又可得到第i次的状态Qi可通过初始状态Q0表示为:

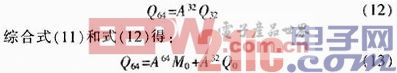

式中状态转移矩阵A可由式(7)和CRC32串行实现框图推导得到。首先32位数据串行输入,与移位寄存器相关位中的初始值进行模2加减运算,32次移位后数据输入完毕,即:

然后再进行32次移位,移位寄存器中的内容即为所求的CRC校验值,则:

由式(13)可知:CRC校验值只与CRC校验初始值M0和需校验数据Q0有关,其中A64和A32可以由MATLAB计算得出。通过计算,可以得出CRC校验最高位为:

4 SATA协议中CRC32算法实现

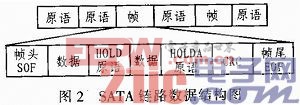

SATA总线主要由应用层、传输层、链路层和物理层组成,其中传输层主要用于传输数据命令,链路层则是对数据进行编码和解码以保证数据在链路中正确传输。SATA总线链路中的信息包含两种结构:原语(Primitive)和帧(Frame),两者都以双字为最小的单位,其结构如图2所示。本文引用地址:http://www.eepw.com.cn/article/159619.htm

帧结构由多个双字组成,包括帧头(SOF)、帧数据、帧尾(EOF)和用于控制码流的控制原语HOLD原语和HOLDA原语。SATA协议中CRC校验模块需自动识别出数据流中的原语,并不计算这些原语的CRC值。在发送信息时,需要由帧数据生成CRC码,即所有非原语数据都要进行CRC编码,并且将生成的CRC值插入到帧尾(EOF)之前进行传输。在接受到数据时,需要对帧数据进行CRC校验,从而判断数据在链路中传输是否出错。在SATA协议中规定CRC校验初始值0x52325032,并且在帧头和帧尾中的数据不能超过2 046个双字。

评论