基于MFRC530设计的ISO14443A无接触读卡技术

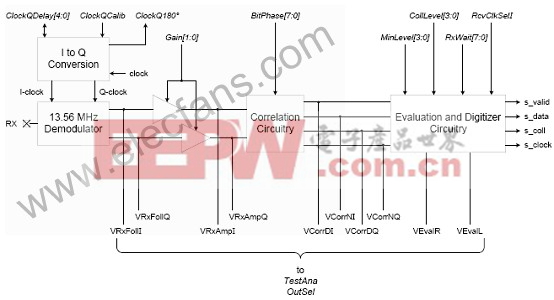

The MF RC530 supports all layers of the ISO14443A communication scheme.

The MF RC530 supports contactless communication using MIFARE® Higher Baudrates.

The internal transmitter part is able to drive an antenna designed for proximity operating distance (up to 100 mm) directly without additional active circuitry.

The receiver part provides a robust and efficient implementation of a demodulation and decoding circuitry for signals from ISO14443A compatible transponders.

The digital part handles the complete ISO14443A framing and error detection (Parity CRC). Additionally it supports the fast MIFARE® Classic security algorithm to authenticate MIFARE Classic (e.g. MIFARE® Standard, MIFARE® Light) products.

A comfortable parallel interface, which can be directly connected to any 8-bit μ-Processor gives high flexibility for the reader/terminal design. Additionally a SPI compatible interface is supported.

MF RC530主要特性:

Highly integrated analog circuitry to demodulate and decode card response

Buffered output drivers to connect an antenna with minimum number of external components

Proximity operating distance (up to 100 mm)

Supports ISO 14443A

Supports MIFARE® Dual Interface Card ICs and supports MIFARE® Classic protocol

Supports contactless communication with higher baudrates up to 424kbaud

Crypto1 and secure non-volatile internal key memory

Pin-compatible to the MF RC500, MF RC531, SL RC400 and CL RC632

Parallel μ-Processor interface with internal address latch and IRQ line

SPI compatible interface

Flexible interrupt handling

Automatic detection of parallel μ-Processor interface type

Comfortable 64 byte send and receive FIFO-buffer

Hard reset with low power function

Power down mode per software

Programmable timer

Unique serial number

User programmable start-up configuration

Bit- and byte-oriented framing

Independent power supply pins for digital, analog and transmitter part

Internal oscillator buffer to connect 13.56 MHz quartz, optimised for low phase jitter

Clock frequency filtering

3.3 V to 5 V operation for transmitter (antenna driver) in short range and proximity applications

3.3 V or 5V operation for the digital part

图1.MF RC530方框图

评论