由外部总线访问MPC5554的内部存储器

3 系统设计

3.1 硬件设计

主芯片使用处理器MPC5554,其内部Flash有2 MB,通过EBI模块进行外部访问。外部主机使用Altera公司生产的Cyclone II系列FPGA芯片EP2C35F672,芯片的I/O资源丰富,选用的672引脚封装最大可用I/O为475个,对于I/O需求很多的应用非常适合。EP2C35F672的33 216个LE单元,105个M4K的RAM块,可以满足较高要求的应用。

电路板上的电源种类较多,MPC5554需要有5 V、3.3V、1.5 V供电,EP2C35F672需要3.3 V和1.2 V供电,外部输入则为5 V。采用2片LT1765将5 V转换至3.3 V和1.2 V,1.5 V则利用NJD2783从3.3 V处生成。

根据图1所示的连接,将MPC5554的EXTAL、TS、TSIZ[0:1]、ADDR[8:31]、DATA[O:31]、RD_WR、BR、BG、BB、TA、TEA等信号线全部接至FPGA的I/O处,其中EXTAL需要引至FPGA的PLL输出口作为外部输入时钟,其余的都接至普通I/O。

为了方便调试及观察结果,将MPC5554的1路SCI接口引出,通过MAX3232电平转换至RS232电平,然后连至PC上的串口,使用超级终端程序进行观察。

3.2 软件设计

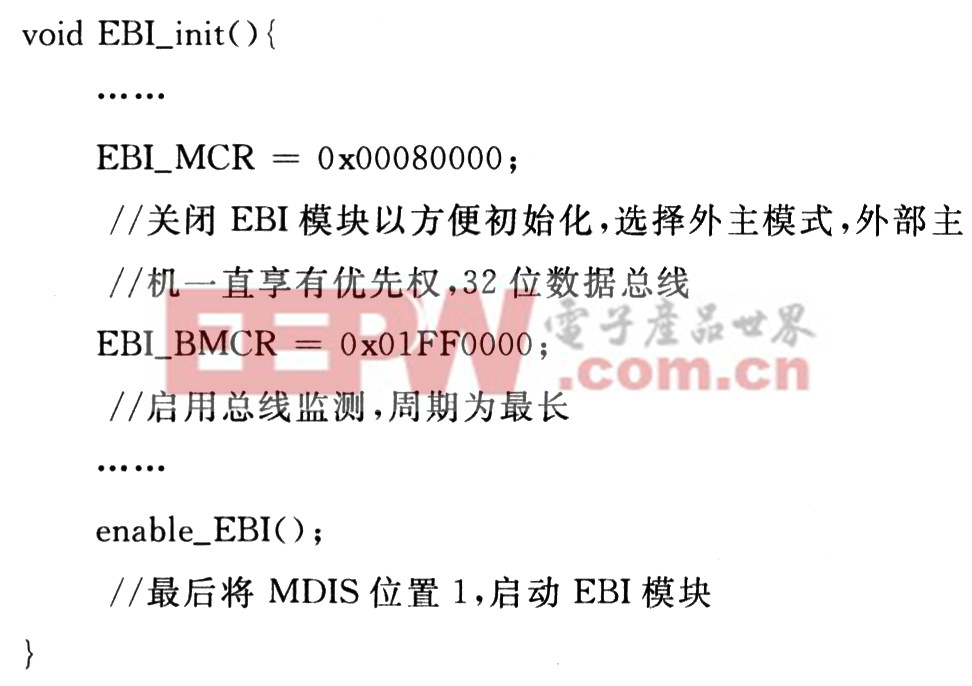

软件的设计需要MPC5554与FPGA协同工作。首先需要将MPC5554配置为外主模式,在MPC5554的EBI模块里共有2个主要的配置寄存器,分别是EBI模块配置寄存器EBI_MCR和EBI总线监控寄存器EBI_BMCR。

EBI模块配置寄存器负责整个模块的基础配置,MDIS位控制EBI模块是否启用,EXTM位配置EBI是否为外主模式,DBM位控制。EBI为32位或16位数据总线,EARP[O:1]用来设置总线请求的优先级。

EBI总线监控寄存器负责对总线监测控制,BMT[O:7]位为总线监测的超时周期,BME位控制总线监测的使能。

另外,还有一个总线传输错误状态寄存器EBI_TESR,TEAF位为传输错误标志位,BMTF为总线监测超时标志位。

EBI模块的初始化程序为:

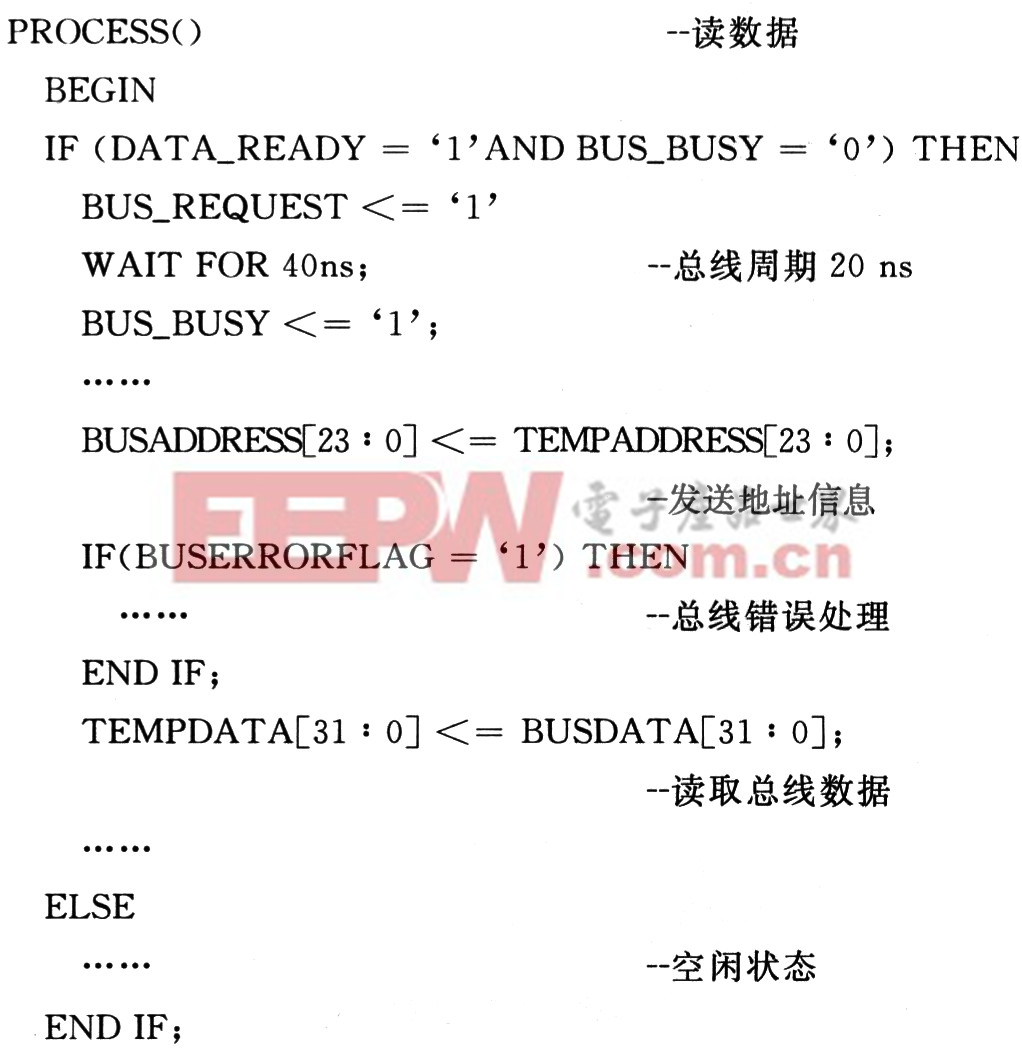

在读取操作时,EBI模块在接收到FPGA发来的地址信息后,返回相应地址的数据信息;在写入操作时,EBI模块根据FPGA发来的地址信息,将数据信息写入相应地址。根据图2~图5的流程与时序,作为外部主机的FPGA起到发起数据传输并结束的作用。FPGA部分使用VHDL语言,只附上结构体里的process部分。

结 语

本文所述的基于MPC5554和FPGA的测试系统已调试完成,MPC5554内部的Flash存储器可以通过EBI模块由外部的FPGA进行读写。与外挂的存储器相比,通信读/写速度和系统的可靠性都大大提高。在实际应用中,其他处理器也可以像文中的FPGA一样模拟总线时序。当应用中不需要数据传输时,也可将连接配置为普通I/0以作他用,硬件配置灵活。

评论