用CPLD支持多个SD器件

在一个系统中添加多个安全数字 (SD) 器件的需求日益增长。然而,大多数主机器件(如 Intel PXA270、TI OMAP和Qualcomm MSM处理器)都只提供一个SD接口。幸运的是,使用复杂可编程逻辑器件(CPLD)即可使主机器件支持任意数量的SD器件。本文详细讲述一种基于可缩放自动侦测双向多路复用器的设计。

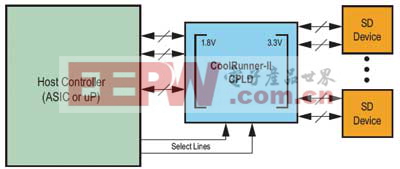

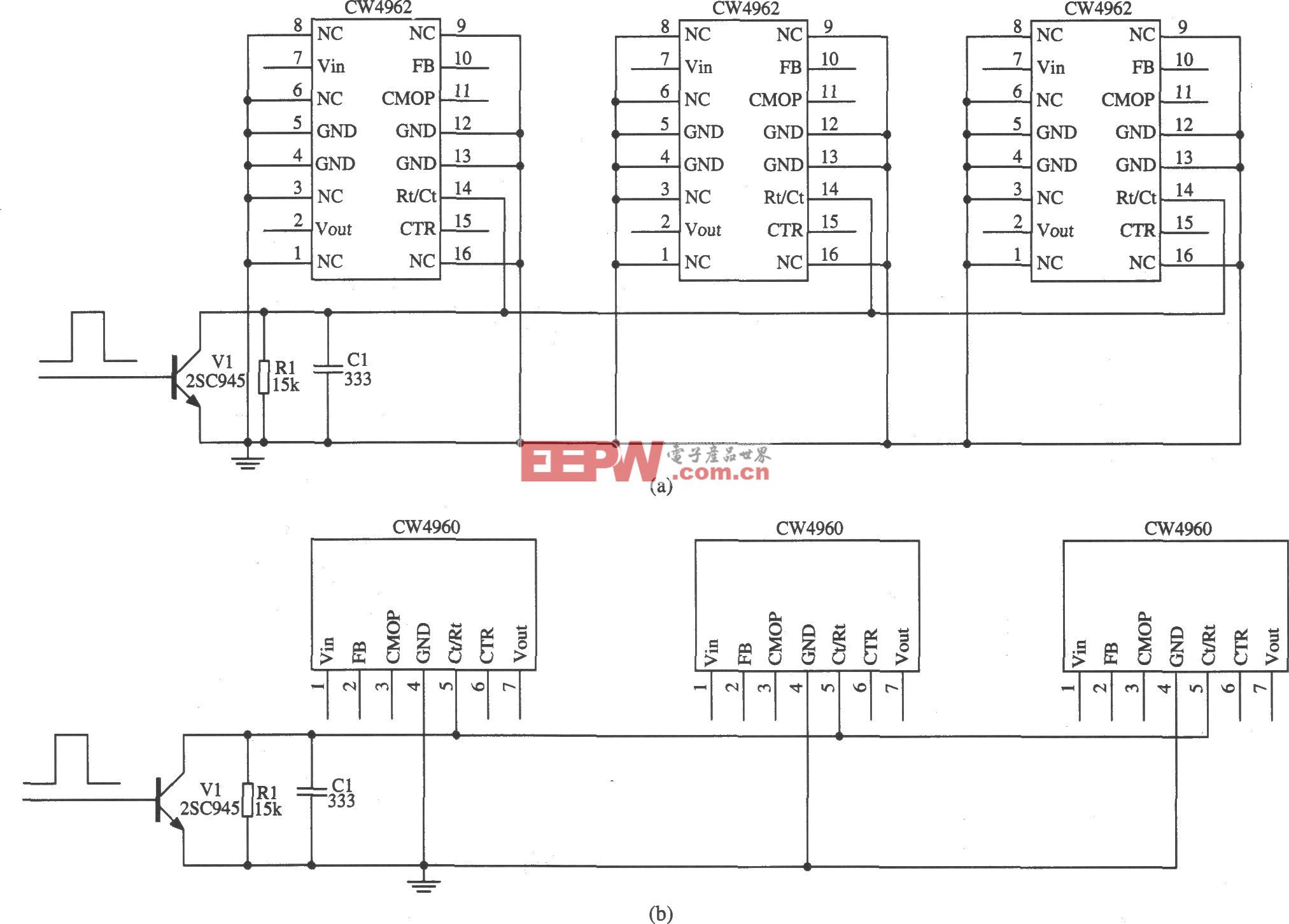

本文引用地址:https://www.eepw.com.cn/article/152101.htm图1所示为通用的CPLD使用模型,可以为仅自带一个SD接口的给定主机器件集成任意数量的SD端口。CPLD处于主机控制器和SD器件之间。这样,CPLD便起到双向多路复用器的作用,使主机器件能够与选定的任意SD器件通信。更重要的是,这种设计没有方向控制引脚,也就是说CPLD自动检测数据流方向。

图1 用CPLD增加SD端口

图1 用CPLD增加SD端口

这种实现方法极其灵活且可缩放,允许随意增减SD端口数量,还支持SPI模式、1位数据模式和 4 位数据模式中任一种定义的SD卡模式。

在此类应用中使用CPLD器件,主要目的是为主机控制器提供更多的SD端口,同时在主机器件与SD卡之间实现电平转换和逻辑隔离。图1所示为主机器件是1.8V而 SD器件是3.3V的情形。业界最新CPLD的待机电流微不足道,而动态功耗极低。因此,在系统中集成一个复杂可编程逻辑器件不会显著影响功率预算。

符合SDA规范

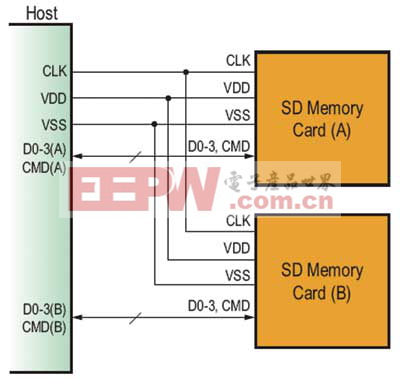

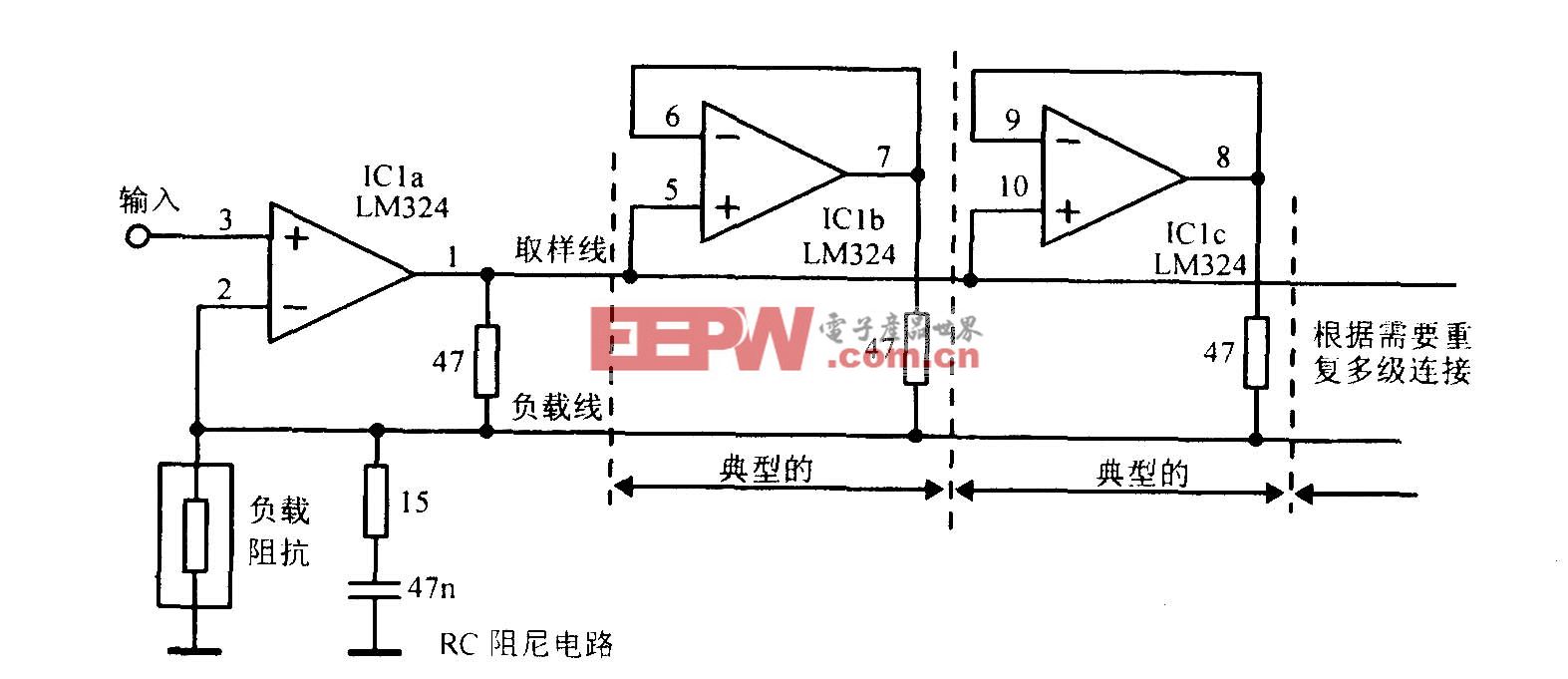

根据SDA(安全数字协会)规范,一条SD总线只能支持一个SD器件。时钟引脚可以共用,但DAT[3:0]和CMD线则必须由每个SD器件独占,如图2所示。

图2 SD系统总线拓扑结构

此参考设计完全符合SDA规范。下面介绍当使用只有一条总线的控制器支持任意数量的SD 器件时如何满足上述要求。

CPLD设计

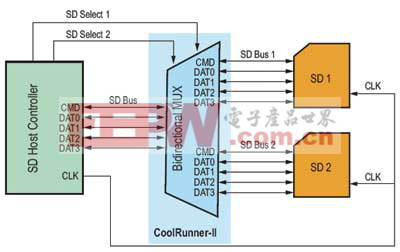

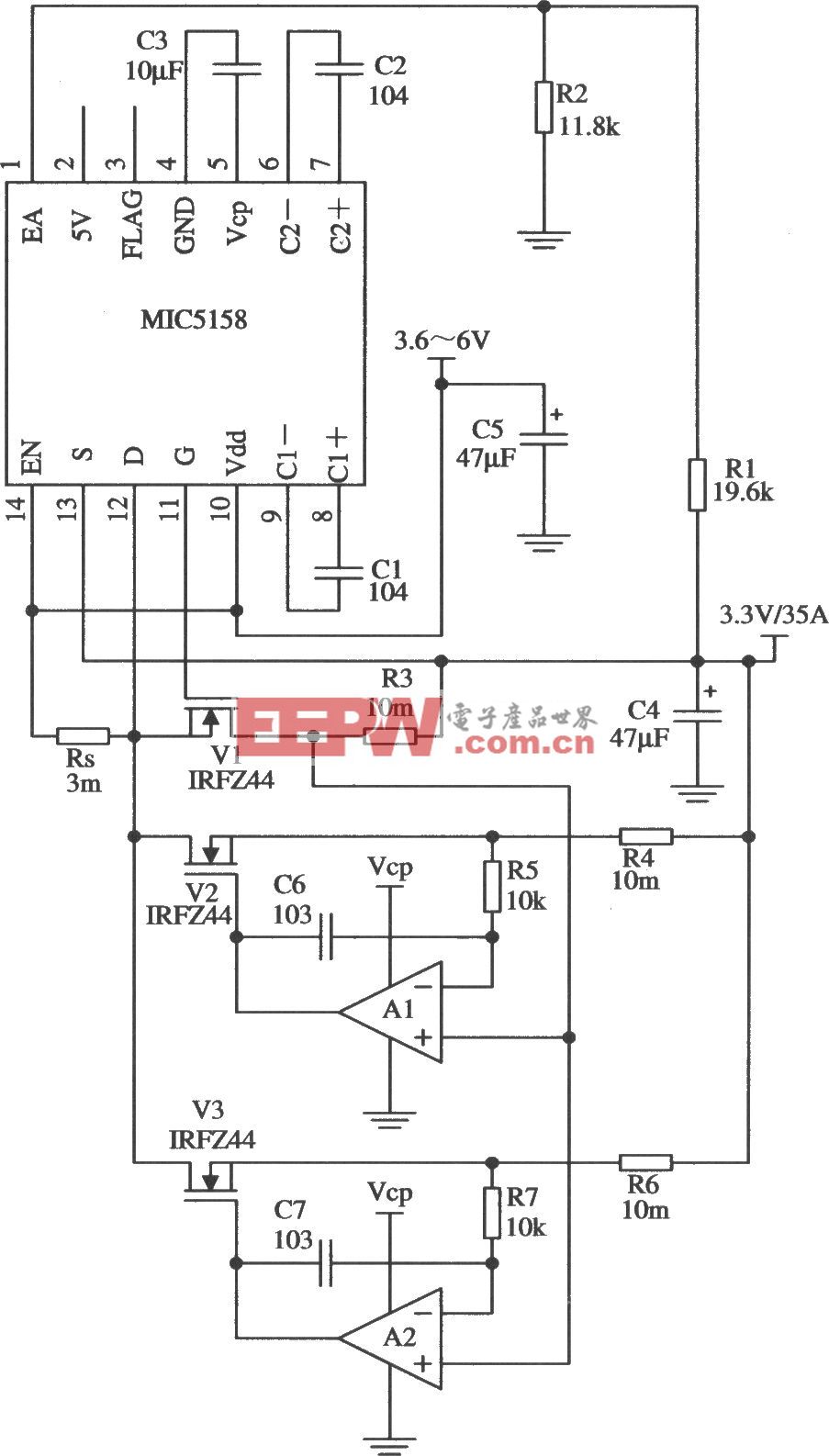

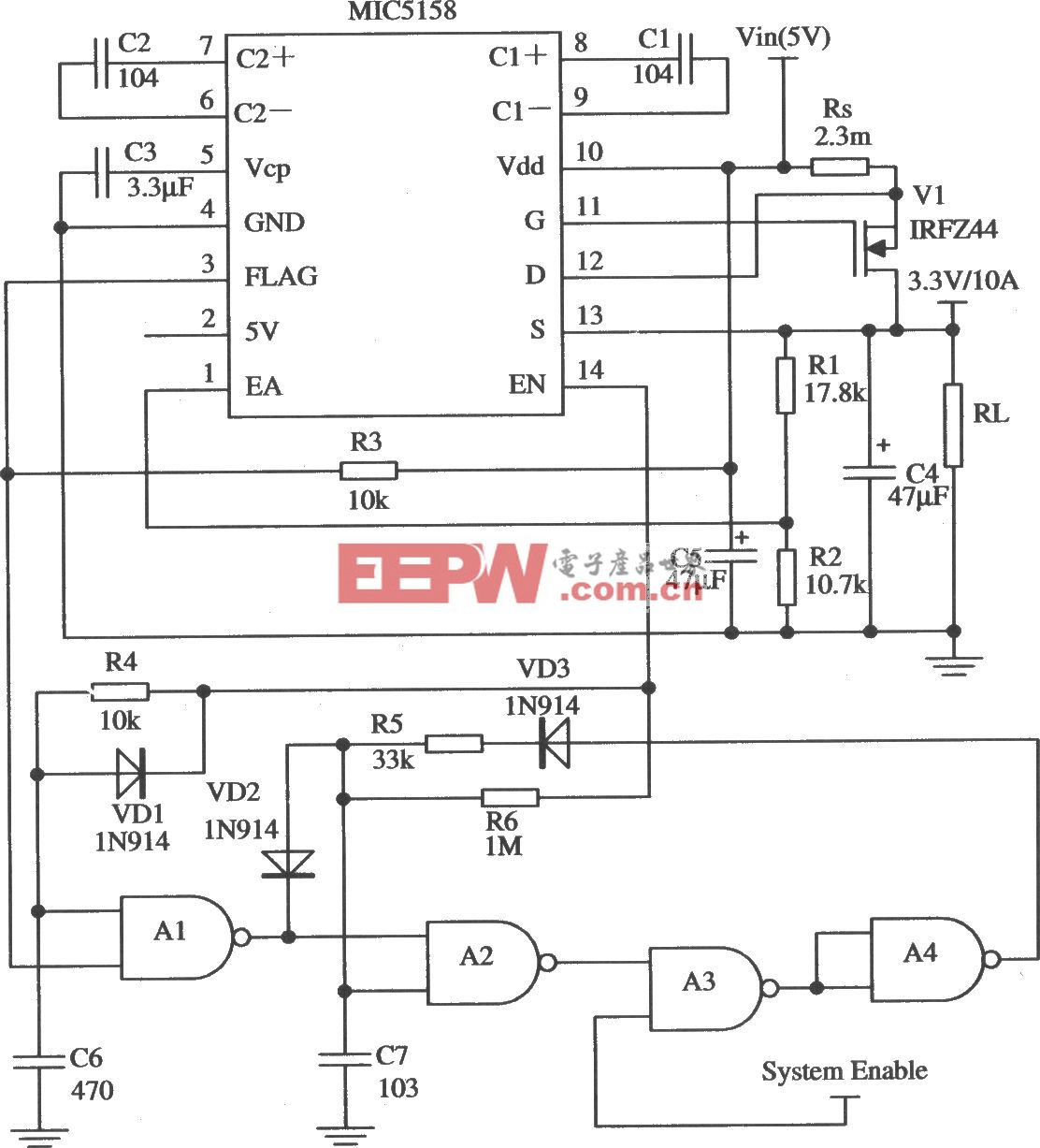

图 3 所示为用此设计实现两个SD器件共用同一SD主机接口时的典型用法。从概念上讲,可以将这种设计视为和用作双向多路复用器。主机器件通过“选择”信号控制CPLD,从而指示与哪个SD器件通信。一旦选中某个SD器件,CPLD器件中的逻辑便自动检测数据流的方向,并且让数据相应流动(从主机器件流向SD卡,或者从SD卡流向主机器件)。此设计不需要方向控制引脚,因此使用方便。

图3 模块级图:双向多路复用器

当多路复用器相应切换时,主机器件可分别访问各SD器件,而不会影响另一SD器件的状态。如果主机器件和SD器件都未驱动数据,则CPLD让系统处于默认的呈弱上拉状态的高阻抗。此电路的主要用途是加强主机器件的SD能力,但也可用此电路提供电平转换和/或逻辑隔离。

实现细节

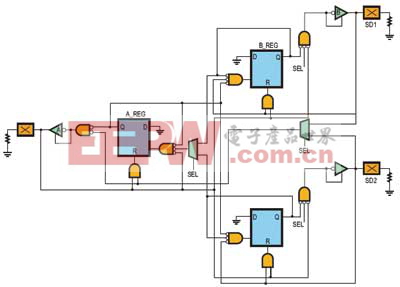

图4所示为1:2双向多路复用器设计的实际逻辑电路,该设计可用VHDL语言描述。在初始或空闲状态下,主机器件和SD卡应处于呈弱上拉状态的高阻抗。因此,图4中的电路设计成对 CPLD的输出缓冲器进行三态控制,从而使外部上拉电阻起作用。寄存器A (A_REG)和寄存器B (B_REG)都设计成在上电时初始化为逻辑“0”。

图4 两个SD器件的SD多路复用器电路

通过向 CPLD 输入“选择”信号来选择SD卡。当“选择”信号为逻辑“0”时选择SD1,而当“选择”信号为逻辑“1”时选择SD2器件。为电路叙述简明起见,我们假设在以下讨论中主机器件只选择与SD1通信。

此设计的自动方向控制方面的实现方式为:当主机器件与SD1器件二者之一置为低时启动事务。例如,如果主机器件准备向 SD1 器件传送数据,则主机器件通过将A侧置为低来开始传送。在置为低时,电路中的逻辑检测到置低的下降沿,并且通过启用“B”输出缓冲器置为有效来响应,而“A”输出缓冲器仍保持无效状态。尤其是当A置为低时,会向A_REG的时钟输入传送一个上升沿。继时钟控制之后,A_REG的Q输出变为逻辑“1”,从而阻止B_REG接收时钟控制事件。当A变为低时,逻辑门B1在A_REG时钟控制与触发的同时输出一个逻辑“1”。这样便可启用“B”输出缓冲器,而B最终会跟随A置为低。

反之,当A从低转为高时,逻辑门B1输出一个低信号,对B输出缓冲器进行三态控制。这样便通过外部上拉电阻强制B变为高。一旦A侧和B侧都变为高,则A_REG和B_REG 复位到0。此过程无限次重复。当SD1要向主机器件传送数据时,情况相反。另外,如果主机器件准备与SD2器件通信,则电路的“选择”信号输入置为逻辑“1”,其事件顺序与上述相似。

设计验证

1 仿真结果

对于此电路,用ModelSim进行了广泛的功能和时序仿真,测试激励已经包括在VHDL 下载中。图5所示为部分仿真结果。

在图5的第一部分中,“选择”信号输入保持为低。白色虚线指示“弱1”状态,换言之就是表示上拉状态。在第一个事务中,主机器件尝试向SD1传送数据,SD1随即响应。紧接着,SD1器件尝试向主机器件传送数据,主机器件随即响应。当“选择”信号输入置为低时,会发生类似事件。主机器件向SD2器件传送数据,然后SD2器件向主机器件传送数据。

图5 仿真结果

评论