MPEG-4编码器在BF561上的优化

1 ADSP-BF56l结构特点

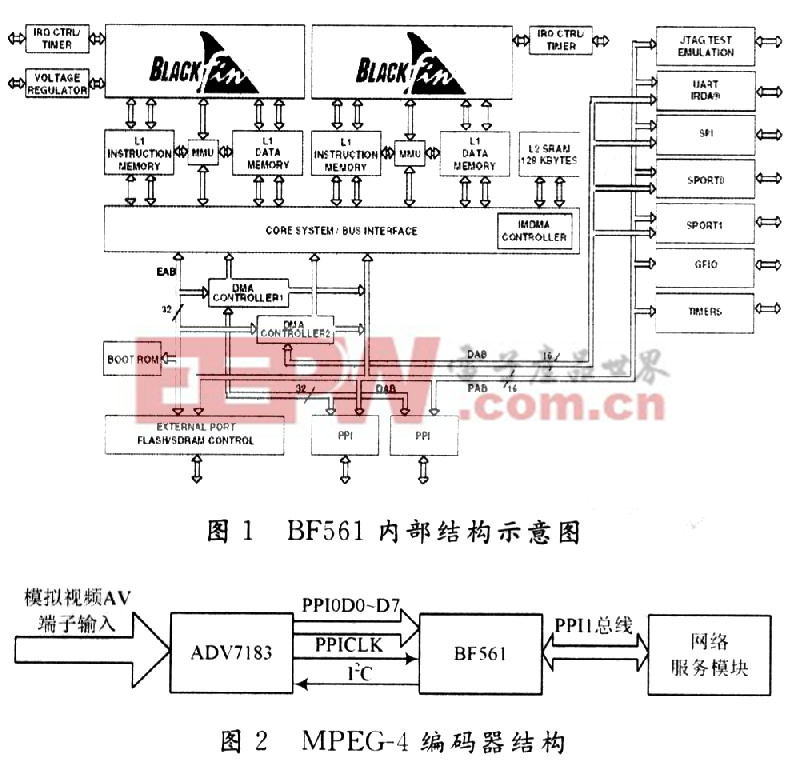

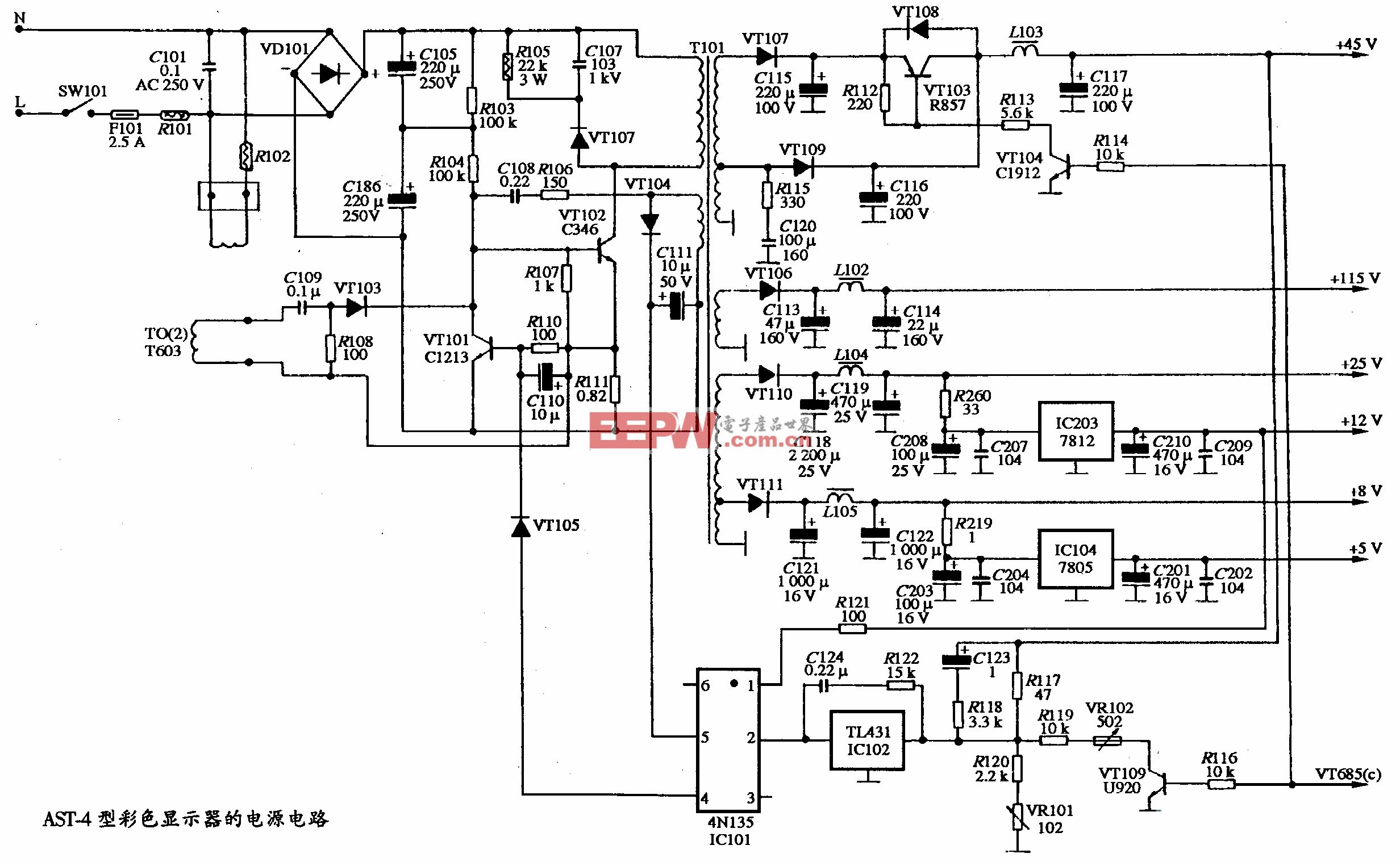

ADSP-BF561是采用对等的双核结构,可以很好地执行两种任务,且开发人员可以随意分配任务来平衡双核之间的负载。如图1所示,每一个Blackfin内核包含两个乘/累加器(MAC),两个40位的ALU,四个视频专用8位ALU和一个40位移位器。运算单元处理来自寄存器组的8位、16位或者32位数据。每个MAC每周期可完成一个16位乘16位的乘法运算,并把结果累加到40位的累加器中,提供8位的精度扩展。ALU单元执行标准的算术和逻辑运算,由于两个ALU具备对16位或32位数据操作的能力,因此运算单元具备的灵活性可以满足各种应用中信号处理的要求。每个32位的输入寄存器可以作为两个16位的寄存器,因此每个ALU可以完成非常灵活的单16位算术运算。通过把寄存器当作两个16位的操作数使用,双16位或单32位操作可以在一个周期中完成。更好地利用第二个ALU,四个16位操作可以简单地完成,加速了每个周期的吞吐量。强大的40位移位器功能丰富,可以对数据进行移位、循环移位、归一化、提取和存储等操作。运算单元所使用的数据来自具有16个16位操作数或8个32位操作数的寄存器组。

同时BF561把存储器视为一个统一的4 GB地址空间,使用32位地址并采用分级存储器结构。Level1(L1)存储器一般以全速运行,没有或只有很少的延迟。Level 2(L2)/Level 3(L3)分布在片内或片外,对它的访问会耗费多个处理器周期。在L1级,指令存储器只存放指令,两个数据存储器存放数据,一个专用的临时数据存储器存放堆栈和局部变量信息。在L2/L3级可以存放指令和数据。

2 编码器整体结构

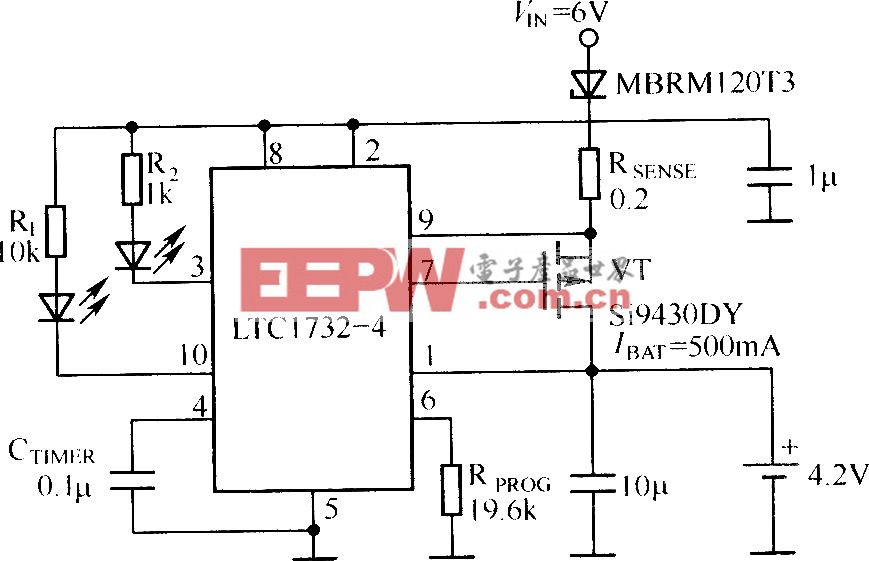

以BF561为核心构成的MPEG-4编码器结构如图2所示,其中BF561为编码处理器,完成视频采集控制以及基于MPEG-4的压缩编码等工作;与之相连的视频解码芯片选用ADI公司提供的ADV7183,它是10位ADC的增强型视频解码器,其内含三个精确模/数转换器(ADCs)和完整的自动增益控制(AGC)电路。BF561与ADV7183之间通过其专用视频接口PPI接口相连,并通过I2C总线协议完成对ADV7183内部寄存器的读/写操作。

评论