超低功耗嵌入式系统设计技巧

摘要:低功耗是嵌入式系统的发展趋势,也是便携式嵌入式设备设计中要解决的关键问题之一。对影响嵌入式系统功耗的因素进行了分析,指出了降低系统功耗的途径,从硬件设计和软件设计两个方面阐述了超低功耗嵌入式系统设计的技巧。

关键词:超低功耗;嵌入式系统;硬件设计;软件设计

无论是在军事还是在商业上的应用,便携式嵌入式系统一般是由可充电电池来供电的,因此,采用有效的节能技巧来改进系统的软硬件设计,降低系统的功耗以增加电池供电设备的使用时间,是便携式嵌入式系统设计中需要研究和解决的关键问题。

1 影响功耗的因素

1.1 集成电路功耗

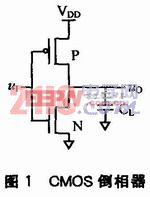

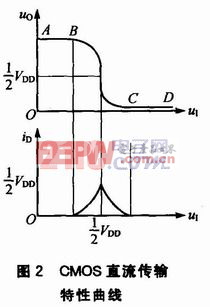

CMOS倒相器在集成电路分析中具有非常重要的意义,常用它来进行集成电路延迟时间和功耗的分析。CMOS倒相器如图1所示,图2是倒相器的直流传输特性曲线。

若电路处在静态(不发生状态翻转)并忽略漏电流的前提下,反相器的功耗几乎为零,如图2中的AB段和CD段。当电路发生状态翻转时,N管和P管具有同时导通的一段时间,此时从电源通过2个管子流向地的电流iD达到一个很高的峰值,如图2对应于BC段的电流。很大的电流意味着较高的功率消耗和热能的损失,这在时钟频率较高时尤为突出。时钟速度越高意味着每秒钟状态的切换次数就越多,也意味着更多的电能损耗。除此之外,在工作时还存在着静态漏电功耗,下面对这2类功耗分别进行分析。

1.1.1 动态功耗

CMOS倒相器从一种稳定工作状态突然转变到另一种稳定状态的过程中,将产生附加的功耗,称之为动态功耗。这一功耗是由2部分组成的,一部分是瞬时导通功耗PT,另一部分是对负载电容充放电所消耗的功率PC,其表达式为:![]()

式(1)中,VDD为电源电压;ITC为2个管同时导通所产生的瞬时电流,不是固定的数值,如图2所示;a为活动因子,表示电容充放电的平均次数相对于开关频率的比值;CL为进行充放电的等效负载电容,包括栅电容、节点电容、互连电容等;f为开关频率,即电路的工作频率。

1.1.2 静态漏电功耗

静态漏电功耗是由亚阈值电流和反向偏压电流造成的。在集成电路中,动态功耗是整个CMOS集成电路功耗的主要组成部分,一般约占电路总功耗的90%以上,静态漏电功耗占电路总功耗的1%以下,因而在大多数情况下可以忽略。

1.2 其他功耗

①纯电阻元件上消耗的功率。电阻为耗能元件,只要电路中使用电阻,就存在着能量消耗。

②有源开关器件在状态转换时,电流和电压比较大,将引起功率消耗。

③非理想元件由于等效电阻的存在而消耗的功率。如电路中的储能元件电感和电容,理想情况下它们是不消耗能量的,但是实际使用的电感和电容都存在着等效串联电阻(ESR),就意味着能量的消耗。

④印制电路板中的走线上消耗的功率,如电源线由于电阻的存在会造成电能的损耗,实际中地线上也存在着电流的流动。由于导线阻抗的存在,串联单点接地的不同接地点之间会存在着电位差,因此在这些地线上也存在着能量的消耗。

评论