TLC5620I与TMS320F2812的接口设计

1 引言

本文引用地址:https://www.eepw.com.cn/article/150665.htm近年来,数字信号处理器(DSP)的应用越来越广泛,其中TMS320F2812作为目前数字控制领域中性能较高的DSP芯片,被广泛应用于电机控制、工业自动化、家用电器和消费电子等领域。由于TMS320F2812本身不具有D/A转换模块,因此在很多需要模拟量输出的控制场合受到限制。所以D/A转换芯片如何与TMS320F2812进行接口,成为数字信号处理系统需要解决的一个重要问题。这里介绍了四路8位电压输出数字一模拟转换器TLC5620I,并给出TLC5620I与TMS320F2812串口接口的软、硬件设计实现方法。

2 TMS320F2812的SPI工作原理

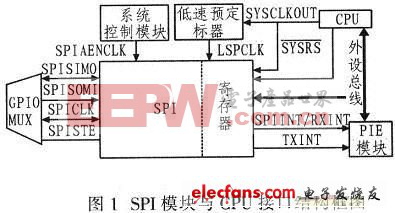

TMS320F2812的SPI模块的9个寄存器用来控制SPI的操作,其中SPICCR设置SPI的软件复位、移位时钟极性字符长度;SPICTL设置SPI的时钟相位、工作模式等;SPISTS中包括溢出标志位、中断标志位等;SPIBRR设置SPI波特率;SPIRXBUF和SPITXBUF为数据接收和发送缓冲寄存器,SP-IDAT用于发送/接收移位寄存器;SPIRXEMU仅用于仿真;SPIPRI控制中断优先级。该器件的SPI接口有一个16级的FIFO,用来减少CPU的开销。图1为SPI模块与CPU接口结构框图。

由图1可知,SPI模块数据传输由40、41、34、35引脚完成,其引脚功能见表1。

TMS320F2812支持125种不同的波特率和4种不同的时钟模式。根据SPI的工作模式(从动或主控),引脚SPICLK可分别接收一个外部的SPI时钟信号或由片内提供SPI时钟信号。

在该设计中,SPI工作在主控模式,SPI时钟由片内的SPI产生并由SPICLK引脚输出。TMS320F2812波特率的设置是由系统的低速外设模块时钟频率LSPCLK和SPI主控制器中的SPIBRR寄存器的值决定的,其计算公式如下:

SPI波特率=LSPCLK/(SPIBRR+1)SPIBRR=3~127

SPI波特率=LSPCLK/4 SPIBRR=0、1、2

引脚SPICLK上的四种不同的时钟模式是由时钟极性位和时钟相位位控制的,其中时钟极性位选择时钟有效沿为上升沿还是下降沿,时钟相位位则设定是否选择时钟的1/2周期延时。四种不同的时钟模式如表2所示。

3 TLC5620I简介

TLC5620I是四路8位电压输出数模转换器(DAC),带有缓冲基准输入端(高阻抗),包含上电复位功能以确保可重复启动,用5 V电源工作。DAC产生范围在基准电压一倍或两倍与地(GND)之间的输出电压,且DAC是单调变化的。TLC5620I使用4个电阻串(resistor-string)来实现D/A转换。每个D/A转换的核心是带有256个抽头的单电阻,分别对应256个可能的代码。每个电阻串的一端连接到GND端,另一端由基准输入缓冲器的输出馈电。通过使用电阻串保持单调性。线性度取决于电阻元件的一致性以及输出缓冲器的性能。由于输入端是经过缓冲的,所以DAC对于基准源总是呈现为高阻抗负载。每一个DAC的输出由可配置增益输出放大缓冲,它可以配置为一倍或两倍增益。

通过简单的3线串行总线可数字控制TLC5620I,此总线与CMOS兼容且易于与所有常用的微处理器作为控制器器件接口。11位的命令字由8位数据(D0~D7),2个DAC选择位(A0、A1)和1个范围位(RNG)组成。后者允许在一倍或两倍输出范围之间作选择。DAC寄存器是双缓冲的,允许完整的新数值组写入器件,然后DAC输出通过LDAC端的控制同时更新。每个通道输出的电压V0由下式计算:

V0=REF×(CODE/256)×(1+RNG bit value)

式中,REF为相应通道基准电压,CODE是从数据位(D7~D0)计算出的十进制数,RNG是范围位串行控制字的0或1。

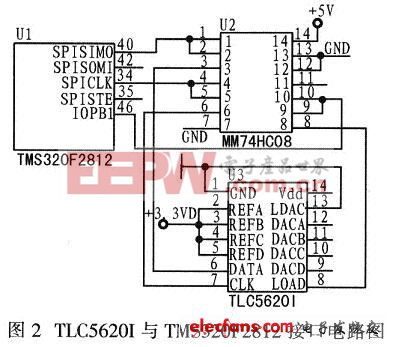

4 TLC5620I和TMS320F2812的接口电路

图2为TLC5620I和TMS320F2812的接口电路。

评论