基于DDS+PLL技术的频率合成器的设计

2.2 方案实施

本设计中AD9852采用串行数据输入模式,在该模式下需要对芯片CS、IO RESET、SDO、SDIO、OSK、I/O UD CLK以及SCLK进行控制信号输入设置。AD9852工作电压为3.3 V,通过将5 V稳压源的输入电压转为3.3 V控制电压,以保证芯片的正常工作,从而防止过高的控制信号输入烧坏DDS芯片。

按照串行控制方式将FPGA与DDS外围电路布置完整,然后通过FPGA进行DDS芯片的初始化。初始化过程中的关键在于,一是对地址与数据的寄存器进行设置,写入各寄存器工作方式所需的控制码;二是初始化串行模式;三是通过串行模式,将FPGA产生的控制码写入到DDS相应的控制寄存器中。

在写地址与数据的寄存器中,主要需要写入的寄存器为frequency tuning word、Delta frequency reaster、update clockrate regis-ter、Ramp rate clock reaster、control register这五个寄存器。其中频率控制字K可按照公式(6)进行计算。

设计中所需产生输出频率为10 MHz,其中N=48,fc=180 MHz,通过公式计算出K=15637498706140转换为十六进制为E38E38E38DC,所以对AD9852的频率控制字寄存器的赋值可表示为data_o=48’hOE38E38E38DC。

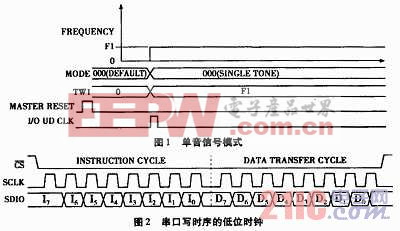

在DDS芯片写数据的过程中,首先,向dds_mareset输入正脉冲信号将DDS复位,然后地址位和数据位分别写入DDS相对应的管脚。在dds_ cs下降沿的触发下,dds_sdio写入可持续八个dds_sclk周期s_wr_inst,该instruction byte决定了接下来的对传输数据读操作或者写操作。经过多次写脉冲操作之后,控制寄存器与频率控制字均写入DDS芯片中,在dds_ioreset的上升沿作用下输出所需频率。如图1、图2所示。本文引用地址:http://www.eepw.com.cn/article/150459.htm

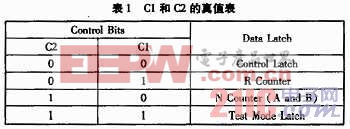

ADF4360-7采用3线串行接口,其数字部分包括24位移位寄存器、14位R计数器以及由5位A计数器和13位B计数器构成的18位N计数器。数据在每个时钟上升沿的作用下移入24位移位寄存器中,并在LE上升沿的触发下,从移位寄存器传输至锁存器中。该锁存器状态由C2和C1两个控制位决定,如表1所示。

低通滤波器相关文章:低通滤波器原理

分频器相关文章:分频器原理 鉴相器相关文章:鉴相器原理 锁相环相关文章:锁相环原理

评论