ADSP21160的电源管理探讨

1引言

本文引用地址:https://www.eepw.com.cn/article/150394.htmADSP21160代码有高度的兼容性,并具有更高的主频和SIMD(单指令,多数据流)功能,现广泛应用于医学、图像处理、军事、工业控制、电信等许多数字信号处理领域,易于实现复杂的实时信号处理。

2.1对+2.5V和+3.3V电源的要求

当ADSP21160工作于80MHz时钟时,内核电源供给VDDINT为+2.5V,最小电压为+2.37V,最大电压为+2.63V,外部口电源VDDEXT为+3.3V,最小电压为+3.13V,最大电压为+3.47V,总电流在1A左右。两套电源供给不应该存在先后顺序,但根据AD公司给出的ADSP21160的40点异常指明:

“IthasbeenfoundinbenchleveltestingwithinADIthatthepowersupplysequencingaffectsthi

sissue.Resultsindicatethatthe2.5Vsupplymustbepoweredbeforethe3.3Vsupplybyaminimumo

f0nsandamaximumof200msandthiswillallowthePLLtoproperlyreset。”所以,要使ADSP21160正常工作,+2.5V电源必须优先于+3.3V电源供给,确保PLL的正确复位。供电的先后顺序,给设计带来一定的困难。在我们的设计实验中,就出现了在仿真调试时,ADSP21160不能正常加载,程序不按预期跳转到指定入口单元的情况。

2.2供电电源的滤波网络

ADSP21160采用了比ADSP2106X更高的主频(80MHz或100MHz)、用独立的电源给内核VDDINT、外部端口VDDEXT和模拟电源AVDD/AGND供电,内核VDDINT和模拟电源AVDD必须满足+2.5V,外部端口电源VDDEXT必须满足+3.3V。

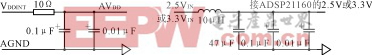

模拟电源AVDD为ADSP21160的时钟产生器PLL供电。要提供比较稳定的电源,必须使纹波干扰比较小。因此,对电源AVDD要经过高质量的滤波网络滤波,如图1所示。

电路板中,该滤波网络应尽量靠近IC引脚。为了避免噪声干扰,模拟地还要求尽可能的粗。

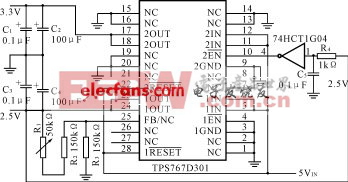

对于+2.5V和+3.3V电源,在ADSP21160的电源入口处,也应该提供一个滤波网络,这可由电容器和磁珠构成,如图2所示。

这里的磁珠和电容器对电源纹波有明显的抑制作用。在某些高频区域内,磁珠的阻抗急剧上升,从而在特定的频率区域内可获得良好的衰减效果,而对ADSP21160的信号传输不会产生影响。

3ADSP21160供电方案

3.1单片ADSP21160工作时的供电方案

ADSP21160工作时的最大峰值电流IDDINPEAK是1.41A,正常情况下其电流消耗也可达0.94A,因此,在设计中必须考虑DC?DCIC输出电流的能力,我们采用TI公司的TPS767D301DCDC[3]IC对单片ADSP21160供电。

TPS767D301是双电源输出,每个电源输出都有单独的复位和输出使能控制。它采用TSSOP封装,输出电流0~1A可调,在1A电流工作时,输出电压降低0.35V。

考虑到这些因素,我们采用了如图3所示的单片ADSP21160的供电电源连接图。当加上+5V电源后,先产生+2.5V输出,然后利用+2.5V作为+3.3V电源输出使能,这样就确保了+2.5V电压的产生优先于+3.3V,使ADSP21160的PLL正确复位。

评论