PCI9656实现与CPCI总线通信的雷达信号处理板

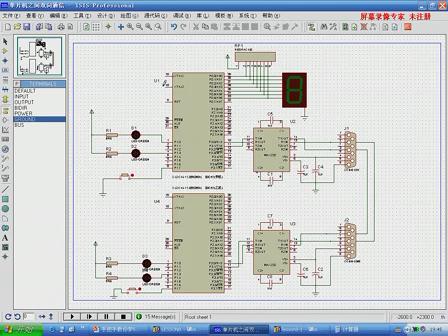

(1)PCI9656使LHOLD变高申请局部总线控制权;FPGA检测到后,立即回应使LHOLDA变高告知PCI9656局部总线申请成功。PCI9656使ADS变低、LW/R变高,然后发送主机地址;FPGAl根据高位地址译码生成DSP片选信号,根据LW/R将主机接口配置为写方式,同时使能PCI9656的READY。

(2)PCI9656检测到READY后,将数据写入双口RAM。数据传输完毕后PCI9656使READY无效,收回LHOLD;FPGAl接着撤消LHOLDA。

(3)FPGAl向相应的DSP发出HBR和WRL申请总线控制权并请求对DSP写数据操作,DSP检测到信号返回HBG和ACK。FPGAl检测到ACK信号后,开始将双口RAM中的数据发送给DSP。数据传输完毕后FPGA使WRL无效,撤销HBR;DSP接着撤销HBG和ACK。此次写操作完成。

4 结 语

提出的基于CPCI总线的高速通用雷达信号处理板设计,继承了CPCI总线可靠、可扩展、通用性强的特点。PCI9656桥芯片和FPGAl逻辑转换芯片实现板外主机对DSP的访问。通过FPGA2将Rocket_IO口与DSP的LinkPort口互联实现数据的高速传输。

评论