EDM安全访问机制应用方案

图表8 AHB bus如何使用hdebug_access和验证逻辑来防止恶意的debug存取

如下verilog code说明了如何使用hdebug_access信号:

//--- Use hdebug_access to prevent malicious debug access in AHB Bus Controller

//* assume zero-wait-state AHB access

…

parameter IRRELEVANT_DATA = 32'hcafe0001;

parameter AUTH_CODE = 32'h01020304;

…

always @(posedge hclk or negedge hreset_n) begin

if (!hreset_n) begin

dbg_acc_d1 = 1'b0;

end

else begin // data phase indication of debug access

dbg_acc_d1 = hdebug_access;

end

end

…

always @(posedge hclk or negedge hreset_n) begin

if (!hreset_n) begin

passcode_reg = 32'd0;

end

else if (passcode_wen) begin //debugger enters passcode through debug access

passcode_reg = hwdata[31:0];

end

end

…

//validate passcode to check authentication

assign auth_check_fail = (passcode_reg != AUTH_CODE);

//return irrelevant data if the authentication check of debug access fails

assign hrdata_out = {32{data_read_en}}

((dbg_acc_d1 auth_check_fail) IRRELEVANT_DATA : normal_data_out);

4.实际的应用

用户经由上面的介绍完成了权限管理逻辑后,并且挂在AndesCoreTMAHB bus上,再经由仿真器(Cadence)仿真此权限管理逻辑的行为,如下面几张图所示:

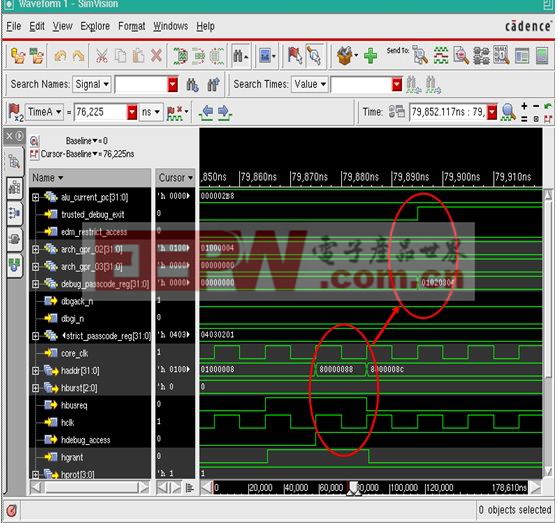

edm_restrict_access信号控制

下图说明由sw code把edm_restrict_access signal disable

图表9 由sw code把edm_restrict_access signal disable

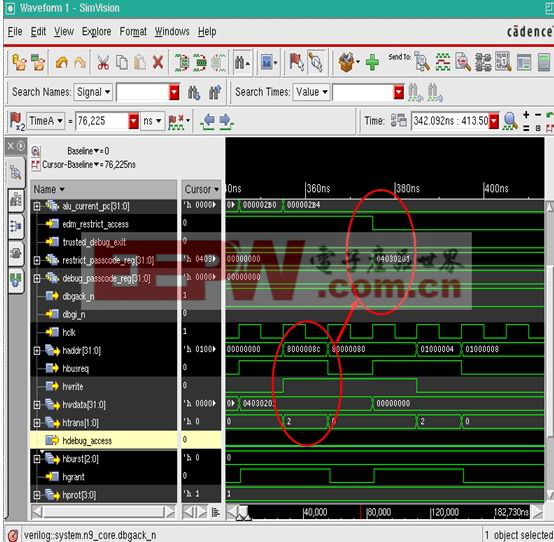

trusted_debug_exit信号控制

图表10 经由debug access把trusted_debug_exit signal设定成high

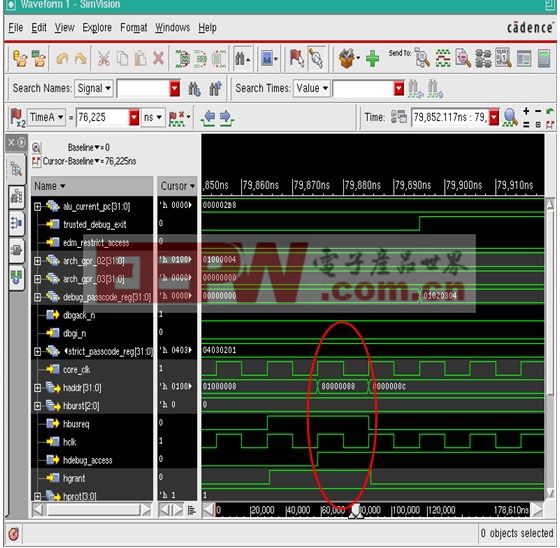

debug_access信号

下图说明经由debug host来做存取时,debug_access signal会从low变成high

图表11 经由debug host来做存取时,debug_access signal会从low变成high

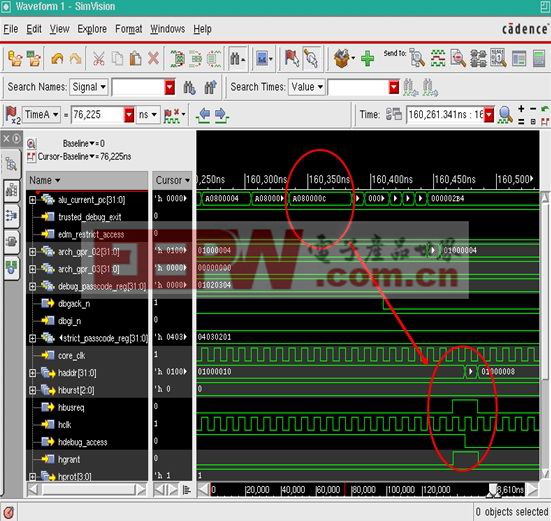

下图说明经由执行IRTE instruction时,debug_access signal会从high变成low

图表12 经由执行IRTE instruction时,debug_access signal会从high变成low

5. 结语

EDM安全存取是AndesCoreTM保护周边装置内容不被窃取的功能,也因为越来越多客户使用到此功能,所以撰写此技术文章让客户更能进一步了解到此功能的用途,让客户能够很快速的上手,并且使用EDM安全存取是一件愉快与简单的工作。

评论