基于多处理器的可识别方位引信信号处理系统

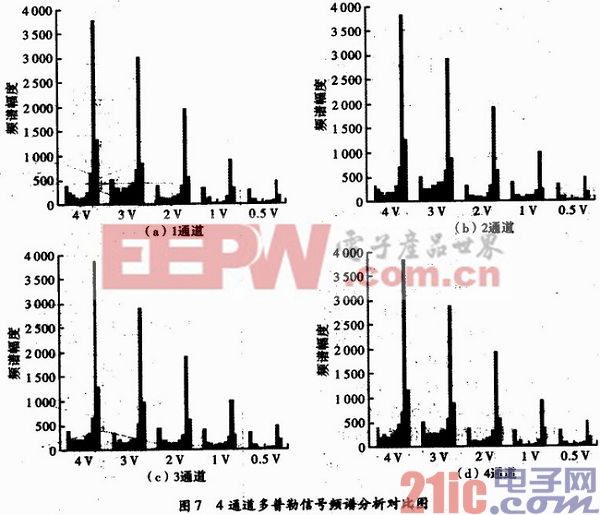

采用多普勒信号最大值比较法来识别目标脱靶方位,即根据4路多普勒信号进行频谱分析后,按照频域能量比幅的方祛进行方位识别,4通道多普勒接收机和信号器多通道处理之间的指标一致性将影响测向的精度,对接收机和信号处理器的通道一致性进行了标定,如图7所示。本文引用地址:http://www.eepw.com.cn/article/148047.htm

3.2 多处理器协同工作下高速数据传输

由于设计中采用FPGA+DSP的系统构成方式,由两片FPGA完成4路多普勒信号的FFT运算、求模运算等,由DSP完成后续复杂算法计算。对于每帧运算,经2片FPGA处理得到的4路信号频域信息能够快速、同步、准确的传到下级DSP芯片中,是多处理器设计中的难点。

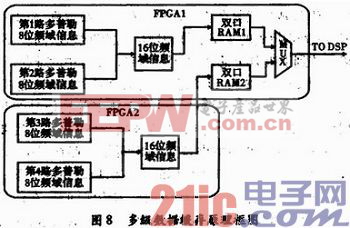

以256点,8位FFT运算为例,在两片FPGA进行完FFT运算和模值运算后,得到4路多普勒信号的频域信息,共4路×256点×8位数据,这些数据后要进行频域单元平均恒虚警算法判断是否存在目标,以及用消比幅算法来判断目标的方位信息。而进行下一步处理,首先要完成4路频域数据的传输问题,在信号处理系统设计中,数据处理有实时性处理的要求,并且FPGA与DSP之间只有一个数据通路,如果将4路数据串行传输,传输时间将大幅增加,直接导致信号处理系统不能满足实时性要求。基于这样的考虑,在传输数据之前首先将4路×256点×8位数据,转化为1路×512点×16位的频域数据,通过DSP的16位数据通路传输数据,这种数据预处理方法需要将两片FPGA的数据进行融合,在缓存模块的软件设计中,首先将FPGA1和FPGA2中的两路FFT运算结果2路×8位融合成1路×16位数据,再将FPGA2中的处理结果传至FPGA1中,将两片FPGA的处理结果分别存入两个双口RAM中,两个存储器统一由DSP地址总线控制,增设存储器选择端,同一时刻仅有一个RAM向DSP传输数据。多级数据缓存示意图如图8所示。

根据上述原理进行数据缓存设计,本系统能够快速、4通道同步、准确地将频域处理结果送制下级运算中,保证了系统的准确性和快速性。

3.3 高速信号处理中的多级流水设计

由于引信与目标高速交会,要正确识别目标、精确控制炸点,就必须在较短的时间内处理大量的回波信息。定向毫米波引信数字信号处理立足于干扰条件下探测识别目标的设计理念,更需要在短时间内对多个象限的回波信号做多批次的处理并进行特征积累,完成干扰模式的识别和目标的精确检测及定位。因此,对信号处理的快速性、实时性要求更高。

为保证系统工作的实时性,在整个信导处理系统设计中采用了多级流水线处理,首先将整个信号处理系统分为时频转换和目标检测、方位识别两级大流水线,在FPGA的设计中,将整个时频转换也分为数据接收缓存、FFT运算、求模运算、数据输出缓存等模块。在每个模块设计中,又将各模块运进行分级处理,多级流水线处埋保证了整个信号处理系统的实时性和快速性。多级流水的思想利用了FPGA内部的丰富资源、面积换取了速度,大幅提高了系统关键路径的最高时钟频率,fmax。

4 结束语

文中设计了一种基于多处理器的数字信号处理机,不仅实现了引信的频域目标检测算法,同时实现了基于多普勒比幅算法的方位识别算法,具有8象限的方位识别能力,信号处理器装调完成后,对信号处理电路进行了不同交会状态的数据回放,结果表明,该信号处理器能够在不同的交会条件下,准确给出目标存在信号和目标方位信息,实现8象限的目标方位识别。

评论