I2C总线通信技术在球形机器人双DSP控制系统中的应用

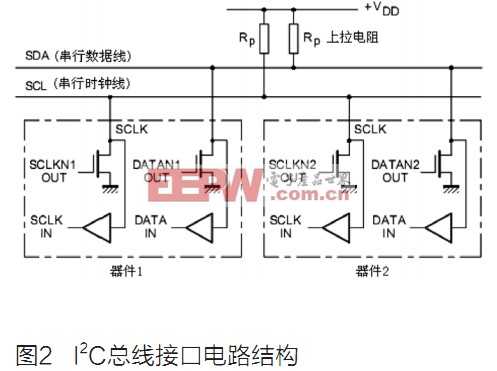

采用I2C总线标准的I2C器件,其内部不仅有I2C接口电路,而且实现了将内部各单元按功能划分为若干相对应独立的模块,通过软件寻址实现片选,减少了器件片选线的连接。CPU不仅能通过指令将某个功能单元挂靠和摘离总线,还可对单元的工作状况进行检测,从而实现对硬件系统简单和灵活的扩展和控制。I2C接口电路结构如图2所示。

本文引用地址:http://www.eepw.com.cn/article/116960.htm

I2C总线上的时钟信号

在I2C总线上传送信息时的时钟同步信号是由挂接在SCL时钟线上的所有器件的连接“与”完成的。SCL线上由高电平到低电平的跳变将影响到这些器件,一旦某个器件的时钟信号下跳为低电平,将使SCL线上一直保持低电平,使SCL线上的所有器件开始低电平期。此时,低电平周期短的器件的时钟由低至高的跳变并不能影响SCL线的状态,于是这些器件将进入高电平等待的状态。

当所有器件的时钟信号都上跳为高电平时,低电平期结束,SCL线被释放返回高电平,即所有的器件都同时开始它们的高电平期。其后,第一个结束高电平期的器件又将SCL线拉成低电平。这样就在SCL线上产生一个同步时钟。可见,时钟低电平时间由时钟低电平期到最长的器件确定,而时钟高电平期由时钟高电平期最短的器件确定。

I2C总线上的数据传输

在数据传送过程中,必须确认数据传送的开始和结束。在I2C总线技术规范中,开始和结束信号(也称启动和停止信号)的定义如图3所示。

当时钟线SCL为高电平时,数据线SDA由高电平跳变为低电平定义为“开始”信号;当SCL线为高电平时,SDA线发生低电平到高电平的跳变为“结束”信号。开始和结束信号都是由主器件产生。在开始信号以后,总线即被认为处于忙状态;在结束信号以后的一段时间内,总线被认为是空闲的。

I2C总线的数据传送格式是:在I2C总线开始信号后,送出的第一个字节数据是用来选择从器件地址的,其中前7位是地址码,第8位是方向位(R/W)。方向位“0”表示发送,即主器件把信息写到所选择的从器件;方向位为“1”表示主器件将从从器件读信息。开始信号后,系统中的各个器件将自己的地址和主器件送到总线上的地址进行比较,如果与主器件发送到总线上的地址一致,则该器件即为主器件寻址的器件,其接收信息还是发送信息则由第8位(R/W)确定。

I2C接口的硬件设计

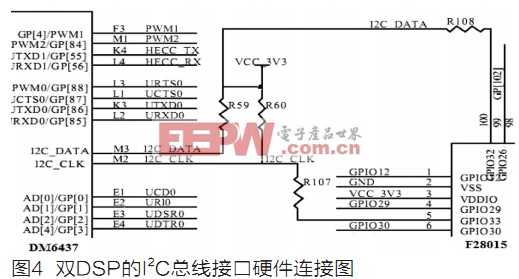

由于DM6437和F28015都支持I2C接口,这使得I2C接口的硬件设计变得非常简单,只需将各自的信号线和时钟线对应相连即可。双DSP的I2C总线接口硬件连接图如图4所示。各引脚连接说明如下:

① DM6437的M3和M2引脚分别对应I2C_DATA和I2C_CLK,而F28015的GPIO32和GPIO33可以分别复用为I2C_DATA和I2C_CLK 。考虑到阻抗不匹配等因素会影响总线数据传输效果,因此还应该在I2C_DATA和I2C_CLK 的直连线路上各串联一个小电阻(R107和R108)。

② 由3.1.1节的I2C总线结构介绍可知,I2C_DATA和I2C_CLK是双向电路,必须都通过一个电流源或上拉电阻连接到正的电源电压。由于DSP的输出CMOS电平为3.3V,所以在硬件设计时将I2C_DATA和I2C_CLK总线通过上拉电R59和R60连接到了3.3V的Vcc电源上。

评论