ESD如何仿真?我找到了ESD仿真的模型

之前的文章“如何理解虚无缥缈的ESD”,有兄弟留言有没有ESD放电的仿真,其实发文前我找过,没找到,所以那篇文章里面的仿真是笼统的给了个信号源,然后按照频谱的方式来分析的。

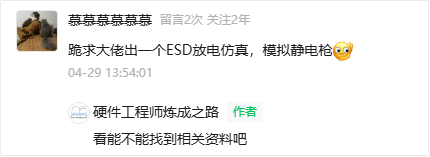

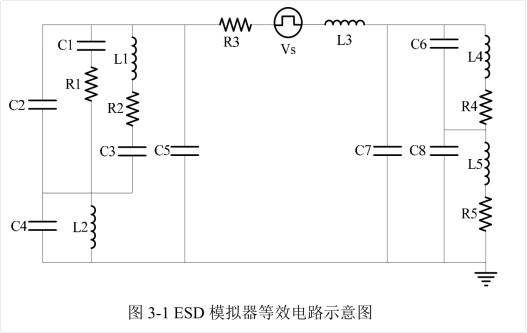

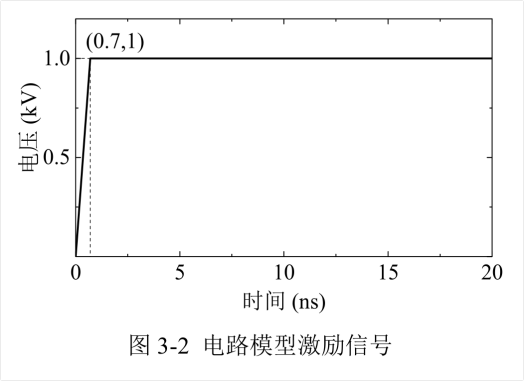

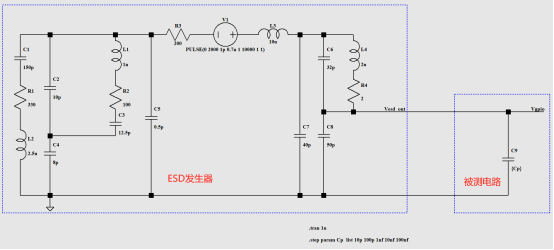

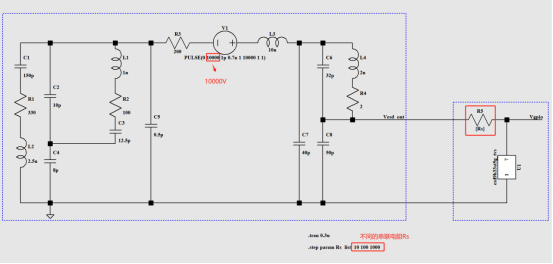

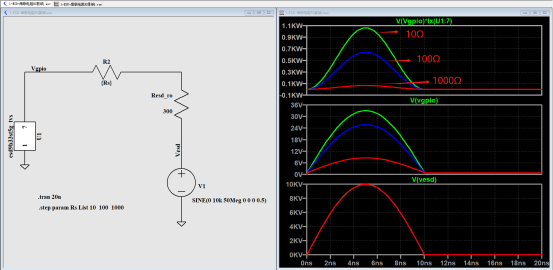

构建电路如下图,左边是ESD发生器(去掉了2欧姆靶电阻和1nh靶电感),右边是被测电路。

构建电路如下图,左边是ESD发生器(去掉了2欧姆靶电阻和1nh靶电感),右边是被测电路。

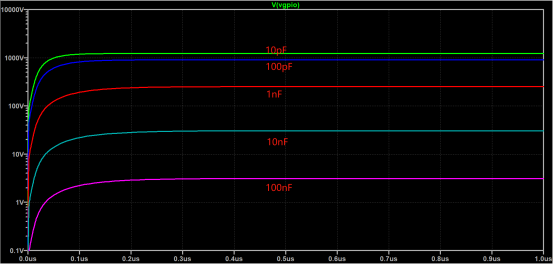

电容值 | 新ESD放电模型2000V测试结果 | 之前文章的频谱分析法2000V结果 |

Cp=10pF | 1220V | 980V |

Cp=100pF | 903V | 180V |

Cp=1nF | 251V | 20V |

Cp=10nF | 30V | 2V |

Cp=100nF | 3V | 0.2V |

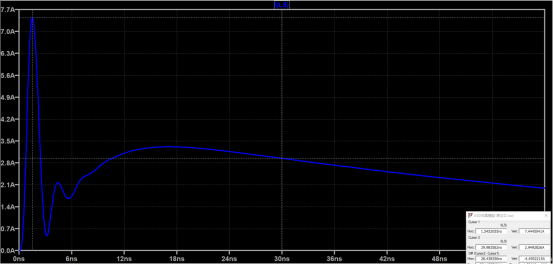

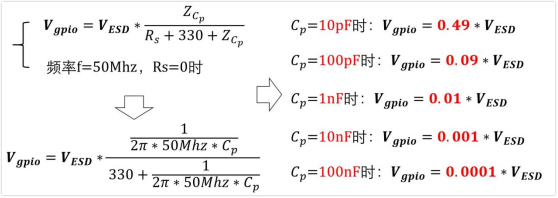

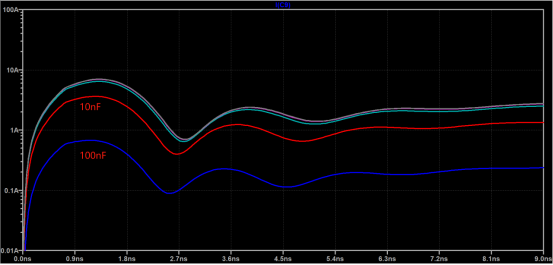

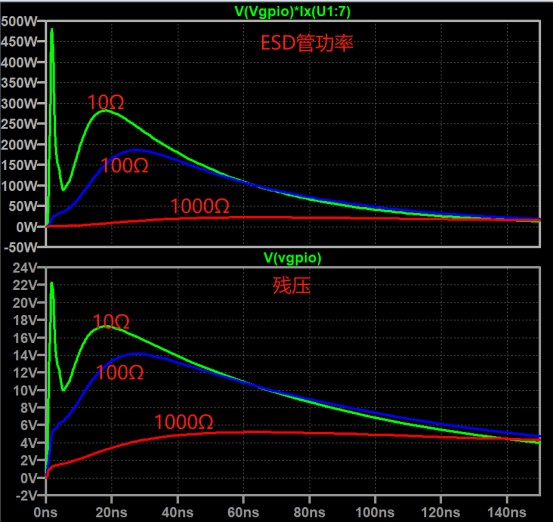

通过对比我们发现,如果只是定性分析,残压Vgpio都是随电容值增大而迅速下降,说明加电容确实对 ESD有用。不过如果定量看的话,二者差异还是很大的,特别是在100nF时,新模型残压是3V,而老的方法只有0.2V,差了十几倍。 为什么会这样呢?到底之前准确还是现在准确? 个人认为,这是因为之前老的方法是从频谱的角度来分析的,而频谱是按照典型放电电流波形来的。而现实的情况是,不同的负载(对不同的东西放电),放电的电流波形肯定是有差异的,之前的模型因其本身假设的局限性,我们得到的结果自然是粗糙的。 因此,总的来说,我认为这个新的模型是更准确的。 下面是新模型静电放电时对应的放电电流波形,可以看到,这个波形和静电放电的典型电流波形差异还是挺大的。由此说明,给不同的负载放电,静电放电电流波形是不同的。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。

关键词:

ESD

仿真

相关推荐

课程4:LTspice 软件基本仿真操作——交流分析与频率响应特性

课程2:LTspice 软件入门与基础操作——元件库与基础电路绘制

芯片引脚及主要特性W78C32B 八位仿真微控制器

ESD防护与电路设计

modelsim最详细最权威的入门教程

加速电路设计的软件

Nexperia展示首款用于EV数据网络的48V ESD保护二极管

面向科学仿真的开放模型系列NVIDIA Apollo正式发布

芯片封装需要进行哪些仿真?

实例分析ESD电磁兼容问题

MOS管输入电阻很高,为什么一遇到静电就不行了?

仪表仿真工具Glstudio

常见 FPGA/PLD及VHDL/Verilog 开发软件

课程1:LTspice 软件入门与基础操作——Tspice 软件简介

如何将第三方模型导入LTspice

Bourns 全新推出可提供 ESD 保护弹性的 TVS 二极管系列,采用节省空间的 DO-214AB 封装

视景建模与仿真工具MultiGenCreator/Vega

仿真自然风控制器

通过确保闩锁保护环来防止ESD

555仿真自然风控制器电路

差分功放仿真电路图

硬件工程师必读攻略-如何通过仿真有效提高数模混合设计性(上)

ESD保护技术白皮书

防静电基础

Ansoft机电系统设计仿真工具

硬件工程师必读攻略-如何通过仿真有效提高数模混合设计性(下)

与 Qorvo 技术对话:推动射频电路仿真

课程3:LTspice 软件基本仿真操作——直流仿真分析

乒乓球游戏电路的CPLD仿真设计电路图

ESD保护电路及PCB设计要点