实验目的(1)熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法;(2)通过实验理解和掌握RS触发器原理;(3)学习用Verilog HDL语言行为级描述方法描述RS触发器电路。实验任务本实验的任务是描述一个RS触发器电路,并通过STEP FPGA开发板的12MHz晶振作为触发器时钟信号clk,拨码开关的状态作为触发器输入信号S,R,触发器的输出信号Q和非Q,用来分别驱动开发板上的LED,在clk上升沿的驱动下,当拨码开关状态变化时LED状态发生相应变化。实验原理基本RS触发器可以由两

关键字:

RS触发器 FPGA Lattice Diamond Verilog HDL

1. 实验目的(1)熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法;(2)通过实验理解和掌握数码管驱动;(3)学习用Verilog HDL描述数码管驱动电路。2. 实验任务在数码管上显示数字。3. 实验原理数码管是工程设计中使用很广的一种显示输出器件。一个7段数码管(如果包括右下的小点可以认为是8段)分别由a、b、c、d、e、f、g位段和表示小数点的dp位段组成。实际是由8个LED灯组成的,控制每个LED的点亮或熄灭实现数字显示。通常数码管分为共阳极数码管和共阴极数码管,结构如下图

关键字:

七段数码管 FPGA Lattice Diamond Verilog HDL

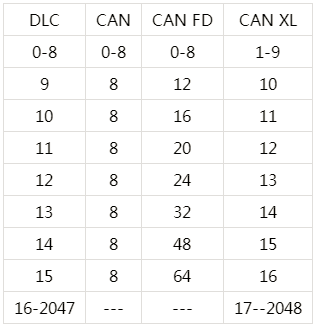

随着信息技术的快速发展,用户应用需求的增加,数据吞吐量越来越大,对CAN总线的通信数据量与通信质量要求也越来越高,那么下一代的CAN——CAN XL会是什么样子的呢?

关键字:

CAN DLC CAN XL

日经新闻报道称,谷歌正在研发Pixel 4/4 XL的5G版本,目前处于试验阶段,尚不清楚谷歌是否会在10月15日与4G版的Pixel 4系列一同发布。

关键字:

谷歌 Pixel 4/4 XL 5G

据外媒报道,东芝存储器美国子公司宣布推出一种新的存储器(Storage Class Memory)解决方案:XL-Flash,该技术是基于创新的Bics Flash 3D NAND技术和SLC,XL-Flash将为数据中心和企业存储带来了低延迟和高性能的解决方案,样品预计将于下月送样检测,或将于2020年量产。

关键字:

东芝 存储器 XL-Flash

当前最流行的硬件设计语言有两种,即 VHDL 与 Verilog HDL,两者各有优劣,也各有相当多的拥护者。VHDL 语言由美国军方所推出,最早通过国际电机工程师学会(IEEE)的标准,在北美及欧洲应用非常普遍。而 Verilog HDL 语言则由 Gateway 公司提出,这家公司辗转被Cadence所购并,并得到Synopsys的支持。在得到这两大 EDA 公司的支持后,也随后通过了 IEEE 标准,在美国、日本及中国台湾地区使用非常普遍。 我们把这两种语言具体比较下: 1.整体结构 点评

关键字:

VHDL Verilog

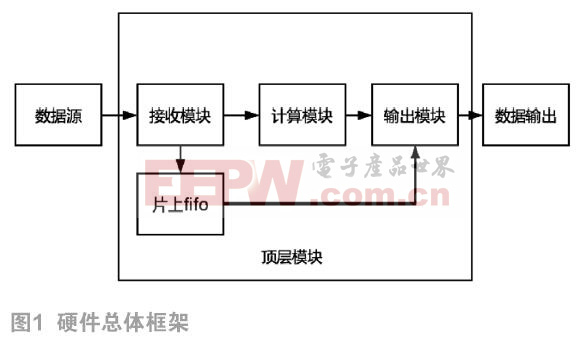

介绍了H.264的量化算法,并用Modelsim进行了仿真,结果与理论完全一致。分析了在FPGA开发板上的资源的消耗。由此可知,完全可以用FPGA实现H.264的量化

关键字:

Verilog 264 AVC

本章介绍Verilog HDL的基本要素,包括标识符、注释、数值、编译程序指令、系统任务和系统函数。另外,本章还介绍了Verilog硬件描述语言中的两种数据类

关键字:

Verilog FPGA

1 功能概述流水广告灯主要应用于LED灯光控制。通过程序控制LED的亮和灭, 多个LED灯组成一个阵列,依次逐个点亮的时候像流水一样,所以叫流水灯。由于

关键字:

流水灯 Verilog fpga

大学时代第一次接触FPGA至今已有10多年的时间,至今记得当初第一次在EDA实验平台上完成数字秒表、抢答器、密码锁等实验时那个兴奋劲。当时由于没有接触到HDL硬件描述语言,设计都是在MAX+plus II原理图环境下用74系列逻辑器件搭建起来的。

后来读研究生,工作陆陆续续也用过Quartus II、FoundaTIon、ISE、Libero,并且学习了verilogHDL语言,学习的过程中也慢慢体会到verilog的妙用,原来一小段语言就能完成复杂的原理图设计,而且语言的移植性可操作性比原理图

关键字:

FPGA Verilog

传统的硬件实现哈夫曼编码的方法主要有:预先构造哈夫曼编码表,编码器通过查表的方法输出哈夫曼编码[1];编码器动态生成哈夫曼树,通过遍历节点方式获取哈夫曼编码[2-3]。第一种方法从平均码长角度看,在很多情况下非最优;第二种方法需要生成完整的哈夫曼树,会产生大量的节点,且需遍历哈夫曼树获取哈夫曼编码,资源占用多,实现较为麻烦。本文基于软件实现[4]时,使用哈夫曼树,会提出一种适用于硬件并行实现的新数据结构——字符池,通过对字符池的频数属性比较和排序来决定各个字符节点在字符池中的归属。配置字符池的同时逐步生成

关键字:

verilog 哈夫曼编码 字符池 FPGA 201712

写verilog代码要有硬件的概念-因为Verilog是一种硬件描述语言,所以在写Verilog语言时,首先要有所要写的module在硬件上如何实现的概念,而不是去想编译器如何去解释这个module

关键字:

verilog FPGA

一个合格FPGA 工程师的基本要求-一个合格的FPGA工程师需要掌握哪些知识?这里根据自己的一些心得总结一下,其他朋友可以补充啊。

关键字:

FPGA Verilog

Verilog设计中的一些避免犯错的小技巧-这是一个在设计中常犯的错误列表,这些错误常使得你的设计不可靠或速度较慢,为了提高你的设计性能和提高速度的可靠性你必须确定你的设计通过所有的这些检查。

关键字:

FPGA Verilog

verilog-xl介绍

您好,目前还没有人创建词条verilog-xl!

欢迎您创建该词条,阐述对verilog-xl的理解,并与今后在此搜索verilog-xl的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473