- 任何信息需要借助声、光、电信 号进行传递,由于光信号和电信号在海水中的衰减比较严重,而声波是人类迄今为止已知的惟一能在水中远距离传播的能量形

- 关键字:

水声通信 CDMA BPSK FPGA

- AI芯片不会是一两颗芯片打遍天下,整体而言,FPGA、GPU、ASIC三大主要AI芯片将在很长一段时间内同时存在。

- 关键字:

ASIC FPGA

- fpga应用的实用电路原理图, FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不

- 关键字:

FPGA

- 摘要: 介绍了精密时钟同步协议(PTP)的原理。本文精简了该协议,设计并实现了一种低成本、高精度的时钟同步系统方案。该方案中,本地时钟单元、时钟协议

- 关键字:

测试 FPGA

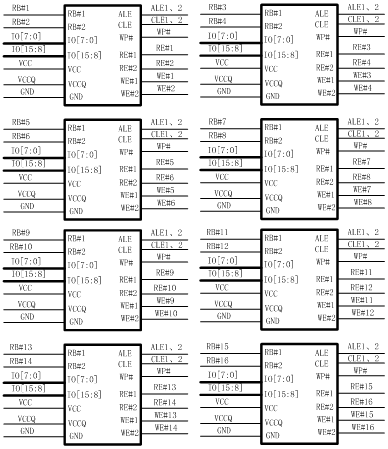

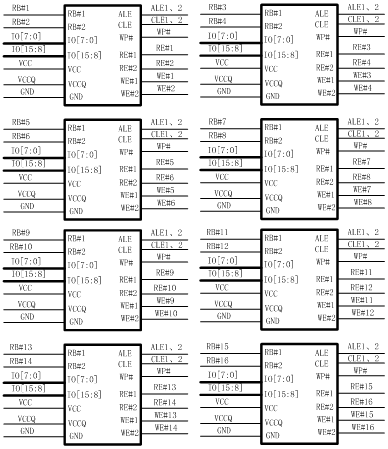

- 1. 引言 NAND FLASH被广泛应用于电子系统中作为数据存储。在各种高端电子系统中现场可编程门阵列(FPGA)已被广泛应用。FPGA灵活的硬件逻辑能实现对NAND FLASH的读写操作。本文中阐述了一种基于NIOS II 软核的NAND FLASH的驱动方法。 2. VDNF2T16VP193EE4V25简介 欧比特公司的VDNF2T16VP193EE4V25是一款容量为2Tb、位宽为16位的NAND FLASH,其内部由8片基片拓扑而成,其拓扑结构如下: 其主要特性如下: Ø 总容量

- 关键字:

NAND NIOS II FPGA

- 上世纪60年代以及70年代早期被认为是ldquo;肌肉车rdquo;时代。这是从中端汽车设计采用大型发动机开始的。最著名的例子包括Chevelles、Fairlanes、G

- 关键字:

FPGA Arria 浮点 OpenCL

- 使用物理不可克隆功能(PUF)确保机器对机器通信安全目前,世界上能够进行机器对机器(M2M)通信的器件数量呈现爆炸性增长趋势。思科公司经常被引用的一项

- 关键字:

FPGA SoC 加密

- 问:本人零基础,想学FPGA,求有经验的人说说,我应该从哪入手,应该看什么教程,应该用什么学习板和开发板,看什么书等,希望有经验的好心人能够给我一些引导。 如果想速成,那就上网看视频吧,这样主要是面对应用的,一个小时内让你的板子运行起来。早期起来的快,活学活用,就是后期没有系统理论支持,会有些吃力,特别是大项目,那完全是个悲剧。国内做的可以的,我知道的就是周立功了,艾米电子也可以吧。这两家都有学习板,不过后者的教程抄袭的前者的。前者功底深厚些,资金不紧张就买前者

- 关键字:

FPGA CAN

- 基于双DSP+FPGA的三相逆变器的设计与实现三相逆变器作为现在一种常用的电力电子设备,对输出电压控制系统需同时实现两个目标:高动态响应和高稳态波形精

- 关键字:

控制 FPGA

- 仿人假手作为肢残患者重获人手功能的主要对象,具有重大的社会需求。理想的假手应具有人手的仿生特征,主要体现在假手构造、控制方式与环境感知3 个

- 关键字:

FPGA 仿人假手

- 目前,随着电力电子技术的发展,高压大容量电力电子变换技术应用越来越广泛,有进一步延伸为我国新的生产力和经济增长点的趋势,其发展前景与计算机信

- 关键字:

DSP FPGA 三电平逆变器

- 在现代电子测量、通讯系统以及生物医学等领域,经常涉及对宽带模拟信号进行数据采集和存储,以便计算机进一步进行数据处理。为了对高速模拟信号进行不

- 关键字:

计算机 FPGA

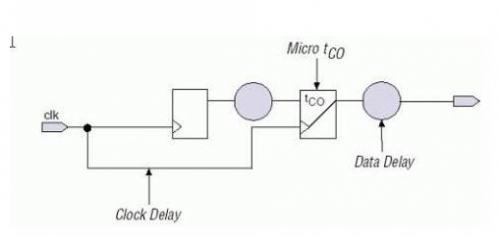

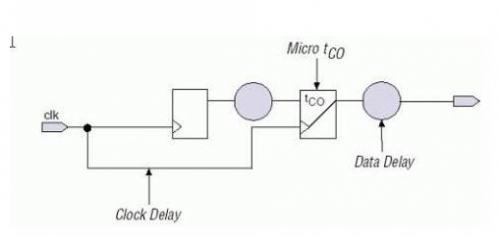

- 从最近一段时间工作和学习的成果中,我总结了如下几种进行时序约束的方法。按照从易到难的顺序排列如下: 1. 核心频率约束 这是最基本的,所以标号为0。 2. 核心频率约束+时序例外约束 时序例外约束包括FalsePath、MulticyclePath、MaxDelay、MinDelay。但这还不是最完整的时序约束。如果仅有这些约束的话,说明设计者的思路还局限在FPGA芯片内部。 3. 核心频率约束+时序例外约束+I/O约束 I/O约束包括引脚分配位置、空闲引脚驱动方式、外部走线延时(Inpu

- 关键字:

FPGA 时序约束

- 引言生物芯片是20世纪末随ldquo;人类基因组计划rdquo;的研究和发展而产生的一项高新技术,是人们高效地大规模获取生物信息的有效手段。目前大部分生

- 关键字:

测量 FPGA

spartan.fpga介绍

您好,目前还没有人创建词条spartan.fpga!

欢迎您创建该词条,阐述对spartan.fpga的理解,并与今后在此搜索spartan.fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473