lattice(莱迪思)半导体公司 文章 最新资讯

SYNPLICITY联手LATTICE将项目扩展到DSP综合技术领域

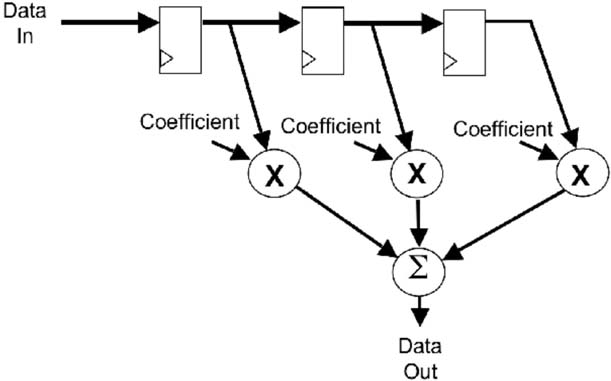

- SYNPLICITY和 LATTICE进一步加强合作,日前共同推出了面向 DSP 设计的高度优化的非专有 ESL 综合流程技术 Synplify DSP。Synplicity 的 Synplify® DSP 软件现可支持 LatticeECP2M 和 LatticeXP2 现场可编程门阵列 (FPGA) 器件,从而为航空航天、无线、电信及数字多媒体应用领域的 DSP 算法实施提供了功能强大的解决方案。 Lattice 公司的市场营销副总裁 Stan Kop

- 关键字: 嵌入式系统 单片机 SYNPLICITY LATTICE DSP MCU和嵌入式微处理器

莱迪思为LatticeECP2低成本FPGA扩展市场

- --第二代 EConomy Plus器件降低了50%的价格并达到双倍的密度 -- 莱迪思半导体公司近日公布了其第二代EConomy Plus 现场可编程门阵列 (FPGA)器件,LatticeECP2系列。用了富士通90纳米CMOS工艺和300毫米硅片,在大批量的情况下,此系列使得FPGA价格降到每1000查找表(LUT)低于0.50美元。与130纳米 LatticeECP FPGA相比,新的系

- 关键字: LatticeECP2 莱迪思 市场

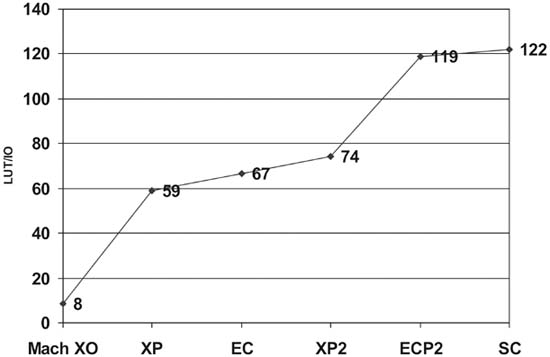

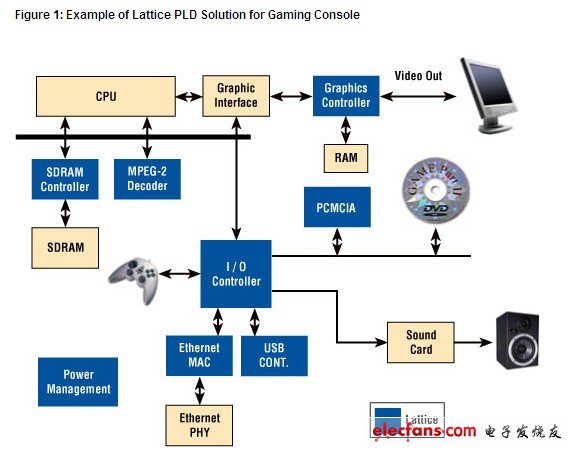

莱迪思富士通发布LatticeSC和LatticeECP2

- -通力合作打造出难以超越的FPGA产品系列- 莱迪思半导体公司近日宣布推出其新一代的90纳米FPGA,包含两个全新的FPGA器件系列。LatticeSC™ 系统芯片FPGA的设计宗旨是提供业界最佳的整体性能,而LatticeECP2™ FPGA则将业界成本最低的FPGA结构和高端的FPGA功能集于一身。这两个器件系列都采用了富士通公司经过优化的工艺,既满足了高容量FPGA对成本效率的要求,又能够提供拥有数百万门的系统级FPGA所需的千兆赫性能。这两个器件系列将在

- 关键字: LatticeECP2 LatticeSC 富士通 莱迪思

用可编程的扭斜控制来解决时钟网络问题的方法

- 时钟网络管理问题提高同步设计的整体性能的关键是提高时钟网络的频率。然而,诸如时序裕量、信号完整性、相关时钟边沿的同步等因素极大地增加了时钟网络设计的复杂度。传统上,时钟网络的设计采用了简单的元件,诸如扇出缓冲器、时钟发生器、延时线、零延时缓冲器和频率合成器。由于PCB走线长度不等而引起的时序误差,采用蜿蜒走线设计的走线长度匹配方法来处理。走线阻抗与输出驱动阻抗的不匹配经常通过反复试验选择串联电阻来消除。多种信号的标准使得时钟边沿的同步更加复杂。至今,这三种挑战会经常遇到,并且鲜有理想的解决方案。以下描述了

- 关键字: 莱迪思

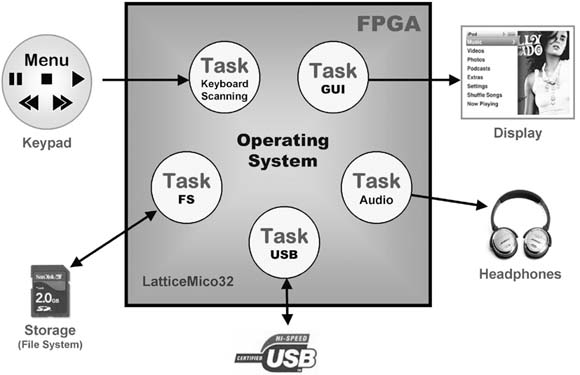

可编程逻辑器件融合CPLD+FPGA最佳特性

- 可编程逻辑器件融合CPLD+FPGA最佳特性 Lattice(莱迪思)半导体公司近日推出了新的MachXO可编程逻辑器件系列产品,Lattice称,这种新一代的跨越式可编程逻辑器件支持传统上由高密度的CPLD或者低容量的FPGA所实现的应用。 据Lattice现场应用支持副总裁Jock Tomlinson介绍,MachXO逻辑器件建立在低成本的130nm嵌入式Flash处理工艺上。它能够在单芯片中瞬时工作,这种特性对于许多CPLD应用来说是十分重要的。3.5ns的管脚至管脚的延时使得器件能够满足当代系统

- 关键字: Lattice(莱迪思)半导体公司

lattice(莱迪思)半导体公司介绍

您好,目前还没有人创建词条lattice(莱迪思)半导体公司!

欢迎您创建该词条,阐述对lattice(莱迪思)半导体公司的理解,并与今后在此搜索lattice(莱迪思)半导体公司的朋友们分享。 创建词条

欢迎您创建该词条,阐述对lattice(莱迪思)半导体公司的理解,并与今后在此搜索lattice(莱迪思)半导体公司的朋友们分享。 创建词条