- quartus的IP仿真错误分析, 大家都知道quartus的IP可以直接拿来用的,大大节省了开发时间,而且其代码是绝对优化的;所有的前奏都操作成功,设置没什么问题,开始对生成的fft.vhd文件进行编译,点击Start Compilation,第一感觉:慢!编译很

- 关键字:

分析 错误 仿真 IP quartus

- 电路的功能为了把大范围的信号电平压缩显示,可使用对数电路,通常称对数放大器,在电气电路中多使用以10为底的常用对数,本电路是1V/十进位、即10倍的变化引起1V变化输出的电路。对数作为除法、乘法等运算电路的基本

- 关键字:

IP 对数 转换电路

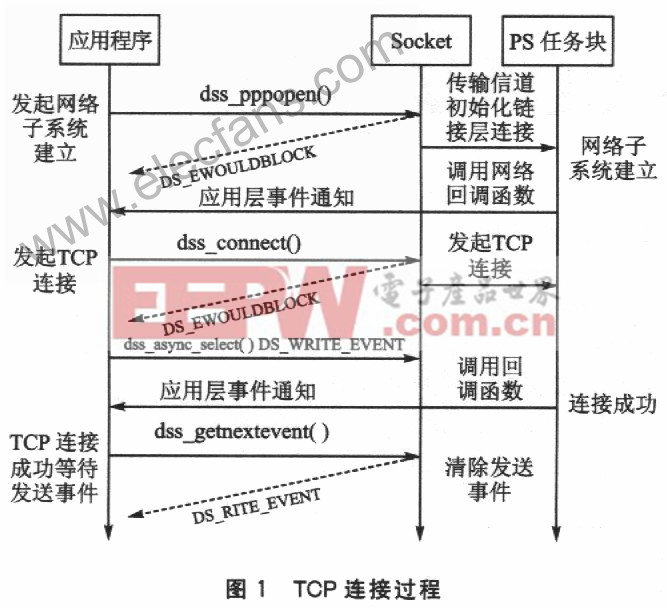

- CDMA是无线通信领域的后起之秀,采用频分编码技术,与基于时分复用的GSM相比具有明显优势。CDMA能够实现从现有通信系统到下一代通信系统的平滑过渡,具有较强的功能伸缩性;可以支持先进的天线技术,通过增加小区覆盖

- 关键字:

协议 介绍 IP TCP 无线 终端 CDMA

- 本文介绍了IP4776CZ38主要特性和优势, 功能方框图, HDMI发送器和接收器应用框图以及PCB布局方案框图.NXP公司的IP4776CZ38是全集成的HDMI接口器件,集成了电平转移,ESD和背驱保护等功能. IP4776CZ38和HDMI 1.3兼容,每路

- 关键字:

4776 HDMI IP 38

- 结合工程实践,介绍了一种利用FFT IP Core实现FFT的方法,设计能同时对两路实数序列进行256点FFT运算,并对转换结果进行求模平方运算,且对数据具有连续处理的能力。设计采用低成本的FPGA实现,具有成本低、性能高、

- 关键字:

FFT Core IP 算法

- 摘要:图形用户界面(GraphicUserInterface,简称GUI)的广泛流行是当今计算机技术的重大成就之一,它极大地方便了...

- 关键字:

Embedded 嵌入式GUI 移植

- 如果适配器模块是由NI公司开发的,那么不需要任何VHDL或其他硬件描述语言的经验。所有的FPGA编程均通过NI LabVIEW FPGA模块和NI-RIO驱动程序软件以图形化的方式完成。如果该适配器模块是由第三方开发的,则或许提供定

- 关键字:

FlexRIO Verilog VHDL IP

- 在计算机整合制造业(CIM)或工业自动化(IA)领域,许多控制设备进行长距离的数据传送时有困难,抗干扰性能不好,多 ...

- 关键字:

TCP IP 远程网络 步进电机 控制器

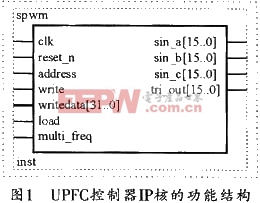

- 0 引言 统一潮流控制器(Unified Power Flow Con-troller,简称UPFC)是一种可以较大范围地控制电流使之按指定路经流动的设备,它可在保证输电线输送容量接近热稳定极限的同时又不至于过负荷。控制系统是UPFC的核

- 关键字:

IP 设计 控制器 UPFC FPGA 基于

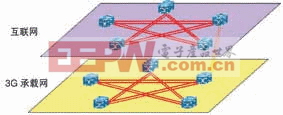

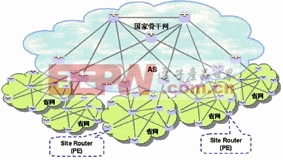

- 毋庸置疑,现代通信网络的发展,是由业务需求和市场需求来决定的,而不是技术的发展。我们回头看看互联网(IP网络)的发展历程,这其中市场推动的痕迹非常明显:这一种六七十年代就已经诞生的IP网络技术,在九十年代

- 关键字:

探讨 规划设计 网络 承载 IP

- 摘要 为降低FPGA实现3电平SVPWM算法的复杂性,减小SVPWM模块所占用的资源,文中利用正弦函数和余弦函数的关系,采用小容量ROM提出了一种新的SVPWM控制算法。利用Verilog HDL实现了算法的硬件设计,并封装成IP核以方便

- 关键字:

SVPWM Nios Core IP

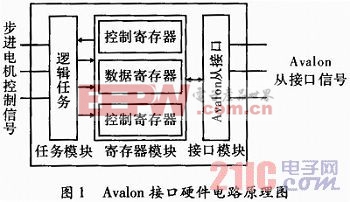

- 摘要 根据Nios II处理器的Avalon总线规范,设计了一款面向步进电机的控制器IP核。该定制IP核采用软、硬件协同设计的方法,功能符合Avalon总线的读写传输时序,具有完备的步进电机驱动能力。仿真结果表明,该IP核具有

- 关键字:

IP 设计 实现 控制器 电机 Nios II 步进 基于

- 毋庸置疑,现代通信网络的发展,是由业务需求和市场需求来决定的,而不是技术的发展。我们回头看看互联网(IP网络)的发展历程,这其中市场推动的痕迹非常明显:这一种六七十年代就已经诞生的IP网络技术,在九十年代

- 关键字:

分析 规划设计 网络 承载 IP

iar embedded secure ip介绍

您好,目前还没有人创建词条iar embedded secure ip!

欢迎您创建该词条,阐述对iar embedded secure ip的理解,并与今后在此搜索iar embedded secure ip的朋友们分享。

创建词条

iar embedded secure ip相关帖子

iar embedded secure ip资料下载

iar embedded secure ip专栏文章

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473