最近的几篇论文都改好投出去了,希望后面有好的结果。暂时也就有点闲暇时间空出来了,好久没有写技术文章来总结提炼一下了,今天难得就写一点。 每年到了找工作的时节,总会有很多迷茫的小本甚至是小硕在到处讯问说:我是不是应该去参加个培训班,去学一门什么什么技术。然后学哪个比较好找工作一点,学哪个收入会高一点等等。每当这个时候就有很多抱着就业目的的人来问到底学什么技术好啊,哪个技术有前途啊,等等。 一般在这个时候,我是不推荐这帮人去学习FPGA的。当然,并不是FPGA技术不好,也不是学FPGA技术没有前途,而

关键字:

FPGA SoC

泸州倍赛达科技有限公司宣布其团队完成了第一项客制化ASIC项目,并于上周投片。 该工程项目是为一欧洲客户定制的,应用为新一代利用光波作数据传输,而且可以在消费或工业终端设备上使用,在单价及功耗这些要素上都必需用ASIC来实现。 此项目在FPGA上作原型机,需要把设计转移至ASIC标准单元(standard cell),而且在功能及性能要与原来的FPGA一致。 美国BaySand总裁兼首席执行官Salah Werfelli先生表示:“此项目将在亚洲某个世界级晶圆代工厂生

关键字:

ASIC

中国济南,2018年3月19日讯,山东高云半导体科技有限公司(以下简称“高云半导体”)今日宣布推出高云 FPGA四路并行离线烧录器(以下简称“离线烧录器”),支持高云半导体小蜜蜂家族GW1N(R)系列芯片数据流文件的离线烧录。 图一 离线烧录器外观图 离线烧录器(图一)是指在脱离PC环境下对GW1N(R)芯片进行数据烧录的设备,具备速度快、数据保密、便携稳定、多路烧录等特点,适用于工厂大批量、快速量产,并方便检修人员外出携带;相比传统的PC终端,离线烧录器优势显著。 其一,离

关键字:

高云 FPGA

2018年一月,赛灵思迎来了第四任总裁Victor Peng。Victor Peng此前担任赛灵思COO(首席运营官),负责赛灵思公司全球销售、产品和垂直市场、产品的开发以及全球运营和质量工作。在此之前,他曾任赛灵思产品执行副总裁兼总经理,负责公司产品组合与差异性技术的定义、开发以及产品市场营销,实现了连续三代核心产品的领先地位,于2017年10月成为董事会成员之一。

关键字:

Xilinx FPGA ACAP

自适应和智能计算的全球领先企业赛灵思公司(Xilinx, Inc.)总裁兼首席执行官(CEO)Victor Peng ,今天揭示了公司的未来愿景与战略蓝图。Peng 的愿景旨在为赛灵思带来新发展、新技术和新方向,打造“自适应计算加速平台”。在该世界中,赛灵思将超越 FPGA 的局限,推出高度灵活且自适应的全新处理器及平台产品系列,为用户从端点到边缘再到云端多种不同技术的快速创新提供支持。 图一 赛灵思CEO Victor

关键字:

Xilinx FPGA

大学时代第一次接触FPGA至今已有10多年的时间,至今记得当初第一次在EDA实验平台上完成数字秒表、抢答器、密码锁等实验时那个兴奋劲。当时由于没有接触到HDL硬件描述语言,设计都是在MAX+plus II原理图环境下用74系列逻辑器件搭建起来的。

后来读研究生,工作陆陆续续也用过Quartus II、FoundaTIon、ISE、Libero,并且学习了verilogHDL语言,学习的过程中也慢慢体会到verilog的妙用,原来一小段语言就能完成复杂的原理图设计,而且语言的移植性可操作性比原理图

关键字:

FPGA Verilog

作为国内领先的可编程逻辑器件供应商,广东高云半导体科技股份有限公司(以下简称“高云半导体”)今日宣布成立香港研发中心,新成立的研发中心位于香港科学园二期浚湖楼,这是继济南、上海、广州、美国硅谷四大研发中心之后,高云半导体成立的第五大研发中心。

“在香港科学园设立研发中心,将为高云半导体在国际市场开拓,创新合作等方面提供重要的技术支持,”高云半导体CEO朱璟辉介绍,“作为一个创新驱动型的公司,高云将在香港打造一个实力雄厚的研发与技术支

关键字:

高云 FPGA

中国香港,2018年3月12日,作为国内领先的可编程逻辑器件供应商,广东高云半导体科技股份有限公司(以下简称“高云半导体”)今日宣布成立香港研发中心,新成立的研发中心位于香港科学园二期浚湖楼,这是继济南、上海、广州、美国硅谷四大研发中心之后,高云半导体成立的第五大研发中心。

关键字:

FPGA 高云半导体

我们(IEEE)最近与Bunny Huang进行了有趣的交流,他是硬件大师以及Chumby,NetTV和Novena Laptop等的创造者。他还是Hacking the Xbox,The Essential Guide to Electronics in Shenzhen两篇文章的作者,在IEEE Spectrum中有两篇专题文章。 我们感兴趣的是Huang的意见,一个小的资金适中的团队,

关键字:

芯片 FPGA

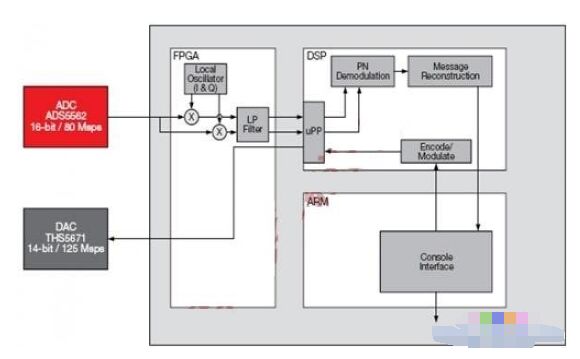

CritICal Link公司的某客户需要针对多个应用开发一个扩频无线电收发器。该客户已经开发出一套算法,准备用于对信号进行调制和解调,但他们却缺少构建完整系统的资源和专业知识。客户希望利用软件定义无线电(SDR)系统的灵活性优势。本文将探讨如何基于德州仪器(TI)的OMAP-L138 DSP+ARM处理器与FPGA来实现该系统。 平台 Critical Link选择其MityDSP-L138F嵌入式系统模块作为SDR的基础,因为该模块不仅具有很强的处理能力,而且可以

关键字:

FPGA ARM

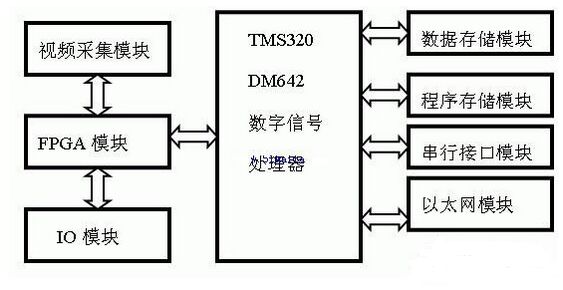

本文将机器视觉与网络技术相结合,使用TI公司新近推出的6000系列DSPsTMS320DM642为核心,应用ALTERA公司的FPGA,用其实现图像预处理,减轻了DSPs的负担。应用网络技术实现图像传输。 1、引言 机器视觉自起步发展到现在,已有15年的发展历史。应该说机器视觉作为一种应用系统,其功能特点是随着工业自动化的发展而逐渐完善和发展的。 目前,国际上视觉系统的应用方兴未艾,1998年的市场规模为46亿美元。在国外,机器视觉的应用普及主要体现在半导体及电子行业,其中大概 40%

关键字:

DSP FPGA

新的一年开启新的希望,新的空白承载新的梦想。这是年初一集微网给读者们拜年时写的寄语。在中国农历新年开年之际,半导体产业里也迎来了许多新的起点。例如长江存储在与苹果就采购前者的Nand闪存芯片一事谈判,又例如前京微雅格副总裁王海力坚守18个月后的二次创业。

2005年年底,即将从清华大学计算机专业博士毕业的王海力加入了一家新成立的中外合资公司——雅格罗技,开始了国产FPGA芯片研发。2010年在北京市政府相关引导资金支持下,该公司也转换身份并更名为“京微雅格&r

关键字:

京微雅格 FPGA

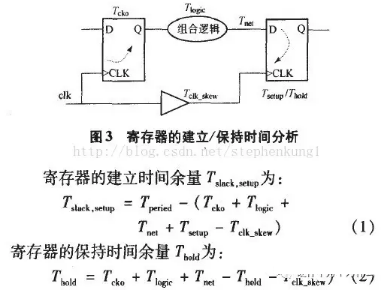

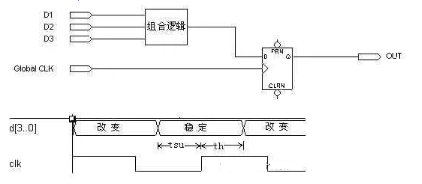

10、FPGA的时序基础理论 我们的分析从下图开始,下图是常用的静态分析结构图,一开始看不懂公式不要紧,因为我会在后面给以非常简单的解释: 这两个公式是一个非常全面的,准确的关于建立时间和保持时间的公式。其中Tperiod为时钟周期;Tcko为D触发器开始采样瞬间到D触发器采样的数据开始输出的时间;Tlogic为中间的组合逻辑的延时;Tnet为走线的延时;Tsetup为D触发器的建立时间;Tclk_skew为时钟偏移,偏移的原因是因为时钟到达前后两个D触发器的路线不是一样长。 这里我们来做如下转

关键字:

FPGA 时序

8、FPGA时钟系统 1. FPGA的全局时钟是什么? FPGA的全局时钟应该是从晶振分出来的,最原始的频率。其他需要的各种频率都是在这个基础上利用PLL或者其他分频手段得到的。 2. 全局时钟和BUFG: BUFG,输入为固定管脚,输出为H型全铜全局高速网络,这样抖动和到任意触发器的延时差最小,这个也就是FPGA做同步设计可以不需要做后仿真的原因。 全局时钟:今天我们从另一个角度来看一下时钟的概念:时钟是D触发器的重要组成部分,一个有效边沿使得D触发器进行一次工作。而更多的时候,D触发器保

关键字:

FPGA 时钟

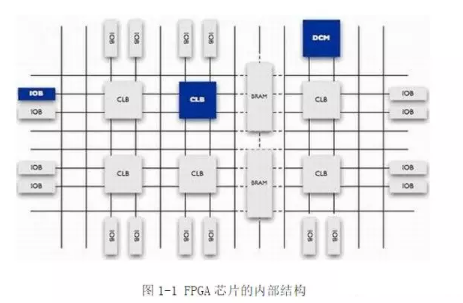

1、查找表LUT和编程方式 第一部分: 查找表LUT FPGA是在PAL、GAL、EPLD、CPLD等可编程器件的基础上进一步发展的产物。它是作为ASIC领域中的一种半定制电路而出现的,即解决了定制电路的不足,又克服了原有可编程器件门电路有限的缺点。 由于FPGA需要被反复烧写,它实现组合逻辑的基本结构不可能像ASIC那样通过固定的与非门来完成,而只能采用一种易于反复配置的结构。查找表可以很好 地满足这一要求,目前主流FPGA都采用了基于SRAM工艺的查找表结构,也有一些军品和宇航级FPGA采用

关键字:

FPGA CPLD

fpga-to-asic介绍

您好,目前还没有人创建词条fpga-to-asic!

欢迎您创建该词条,阐述对fpga-to-asic的理解,并与今后在此搜索fpga-to-asic的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473