- 如今,在各种手持消费电子设备、医疗应用设备、自动售货机/售票机/ATM机、销售终端(POS),工业和过程控制设备中...

- 关键字:

触摸屏 FPGA

- 摘要:介绍了一种高速实时数据采集系统的设计。该系统以FPGA作为逻辑控制的核心,以USB2.0作为与上位机数据传...

- 关键字:

FPGA USB2.0 数据采集

- 0引言在现代电子技术应用领域,A/D转换器是模拟信号转换数字信号的中介,数据采集系统中,一般由单片机或其他...

- 关键字:

AD8341 同步采样 FPGA

- 摘要:利用电子学时间多道存储技术,结合大规模可编程逻辑控制器FPGA和高速大容量双端口内存芯片,设计了一种...

- 关键字:

气溶胶 空气动力学粒径 FPGA

- 电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

- 关键字:

通用平台 协议 FPGA 一致性测试

- Q1:日前Altera与MIPS推出业界第一款的软式核心处理器的FPGA,请谈谈此一产品对于处理器IP与FPGA产业的意义...

- 关键字:

FPGA MIPS SoC Cortex

- 0引言在石油地震勘探中,地震仪通过地震检波器采集信号。地震检波器是为了接收和记录地震波而设计的一...

- 关键字:

光栅地震检波器 DSP FPGA

- 摘要:基于新一代图像压缩国际标准JPEG 2000,介绍一种快速、有效的多层5/3小渡变换的VLSI设计结构,该方法使用两组一维变换实现,用移位-相加代替乘法操作,整体设计采用了流水线设计。利用双端口RAM和地址生成模块

- 关键字:

JPEG 2000 FPGA 离散小波

- 摘要:针对Xilinx FPGA在航天应用中的可行性,文章分析了Xilinx FPGA的结构以及空间辐射效应对FPGA的影响,结合实际工程实践给出了提高其可靠性的一有用办法和注意事项,如冗余设计、同步设计、自检等。表明配置信息

- 关键字:

Xilinx FPGA 辐射 设计技术

- 摘要:文章从FPGA逻辑编程设计技术、EMC技术、高速电路PCB设计技术等几个方面介绍了时统接收处理模块的抗干扰设计及其实现方法,实现了同步脉冲的提取、对时功能、自守时、脉宽调制等功能,提高了同步精度和抗干扰性

- 关键字:

FPGA 模块 可靠性设计

- 摘要:出租车计费系统大多利用单片机进行控制,较易被改装,且故障率较高。针对这一问题,设计了一种基于FPGA的出租车计费系统,可模拟汽车行驶、暂停等待,停止等过程,并可同时显示金额、乘车总路程。设计采用层次

- 关键字:

FPGA 出租车 计费 系统设计

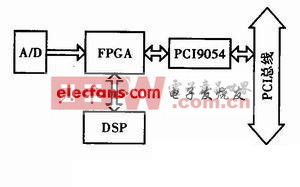

- 本文设计的系统采用PLX公司生产的CPCI协议转换芯片PCI9054,通过Verilog HDL语言在FPGA中产生相应的控制信号,完成对数据的快速读写,从而实现了与CPCI总线的高速数据通信。高速数据传输技术是现代信息技术的前沿科技

- 关键字:

数据通信 CPCI 实现 FPGA 基于

fpga-pwm介绍

您好,目前还没有人创建词条fpga-pwm!

欢迎您创建该词条,阐述对fpga-pwm的理解,并与今后在此搜索fpga-pwm的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473