- 与开发成本很高的ASIC相比,FPGA可重复编程的性能正受到系统设计者的青睐。此外, FPGA的性能和功能也越来越强大,包括32位软处理器、SERDES、 DSP块和高性能的接口。现在的低成本FPGA甚至可以满足大批量的应用。

- 关键字:

FPGA 安全性

- IP视频监控系统市场的增长一直超过预期,并且这种趋势有望延续到2011年。视频监控的应用领域非常广泛,包括:-私...

- 关键字:

FPGA PCIe 视频采集

- 以提供多种基于Flash和反熔丝技术的低功耗、高可靠性单芯片FPGA而著称的Actel公司,在全球经济出现下滑的2008...

- 关键字:

FPGA Flash LCD

- 2004年12月在一项由Synplicity公司委托的调查中,全世界超过20,000名开发者被询问关于他们的硬件辅助ASIC验证...

- 关键字:

FPGA ASIC NRE RTL

- 2009年,赛灵思成立25周年庆典。赛灵思推出全新一代旗舰产品系列——40nm高性能Virtex-6和45nm低成本Spartan-6 FPGA,开启“目标设计平台”新时代。

- 关键字:

赛灵思 FPGA

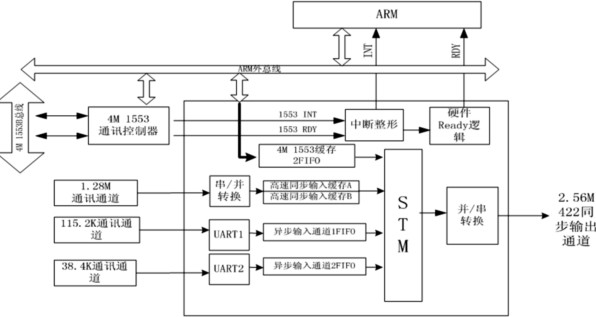

- 现如今,可编程技术在航天领域的应用越来越广泛,在导弹信息采集的过程中,遥测信号源种类增多,信息量加大,而且多路信号源是实时并行输入的,在CPU无法满足要求的时候,可以利用FPGA进行并行数据的采集、缓冲、组帧及实时发送,使图象板更简化、布局更紧凑。

- 关键字:

信息采集 FPGA 组帧 融合 缓冲发送 200904

- 1 引言振动台的作用之一是将被测物件置于振动台上测量其受迫振动时的表现,一般振动台的振动是由振动分析仪控制的,但是由于振动台体积形状和考虑到成本等原因,不利于振动分析仪的研发,所以设计振动模拟器对振动分

- 关键字:

FPGA 振动 模拟

- 过去,医疗设备制造商主要集中于开发诸如X光、MRI和超声波等大型医疗设备。而今天的医疗设备制造商正走向便携医疗电子设备的开发。全球人口老化的不断扩大,以及人们对自身健康状况关注的增加,要求医疗设备实现易于携带和更低成本,以方便在医院之外的其他地方使用。因此,医疗设备制造商几年前就开始开发诸如便携式超声波诊断设备、血压计以及其他使用复杂数字图像处理技术和先进通信技术的个人健康监护等医疗电子产品。

- 关键字:

FPGA 低功耗 便携式 医疗成像

- 文介绍了一种应用于高速数据采集的数字系统,该系统由高速模数转换器FPGA,SDRAM(synchronous dynamicrandomaecess mereory)组成。该系统独立于处理器之外,给处理器预留了总线接口。任何的处理器只要把总线接口连接到此系统上,均可操作。与传统的数据采集系统相比,减少了处理器的控制,而且处理器的处理速度已不再影响系统的性能,提高了速度和效率,具有通用性。本文对高速模数转换器与FPGA的接口实现做了详细的描述,对如何把模数转换器的数据流进行缓冲做了介绍。并对如何在FPGA中

- 关键字:

FPGA 高速数据 采集系统

- 在上世纪最后的十年里,重复可编程逻辑器件大放异彩,在通信行也得到了广泛的应用,这一时期FPGA 竞争基本上集中在容量,性能, IO 标准方面。而在便携应用方面因为FPGA 的高昂的价格,惊人的功耗基本上很少应用。

- 关键字:

ACTEL FPGA 便携式系统 中的应用

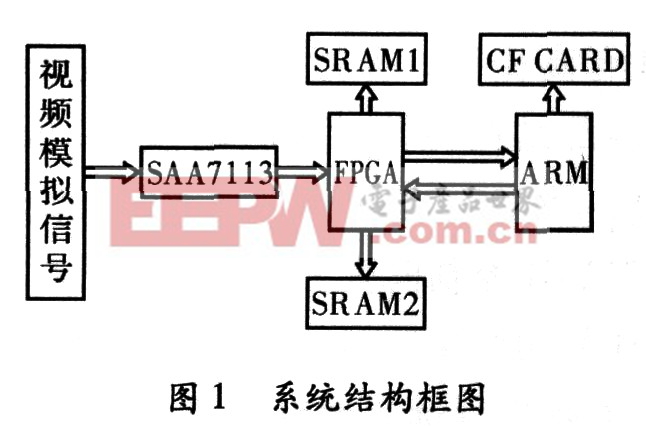

- 基于ARM和FPGA的嵌入式高速图像采集存储系统,文中设计实现了基于ARM和FPGA的嵌入式高速图像采集存储系统,采用双SRAM“乒乓”读写操作和嵌入式CF卡存储等方法,解决了嵌入式图像实时采集存储的难题,提高了图像采集的速度和应用领域,具有实际的使用价值。

- 关键字:

采集 存储 系统 图像 高速 ARM FPGA 嵌入式 基于 视频

- 本文详细介绍了一种新型QAM调制方法,该方法将QAM调制中的相位跳变改为连续变化。仿真实验表明,与普通的QAM调制相比,高次谐波分量大幅下降,同时误码率性能几乎不受影响,可以有效地提高频谱利用率。以FPGA器件为核心设计的连续相位QAM调制器,将绝大部分功能模块由大规模FPGA内部资源来实现,调制器中采用了双通道设计,成功实现了过渡区相位与主要区间相位的交替产生。

- 关键字:

FPGA QAM 相位 调制技术

- 随着电池供电和功率敏感应用的急剧增长刺激了全球对低功耗半导体的需求,设计人员正逐渐发现需要采用低功耗可重编程解决方案来适应不断演进的标准和技术;加快上市速度,并提供下一代前沿硅解决方案所需的封装和功耗性能。对于当前采用可编程逻辑技术的设计人员来说,确定哪一种是最佳器件主要取决于功耗、性能、逻辑和I/O数量等设计约束。

- 关键字:

FPGA

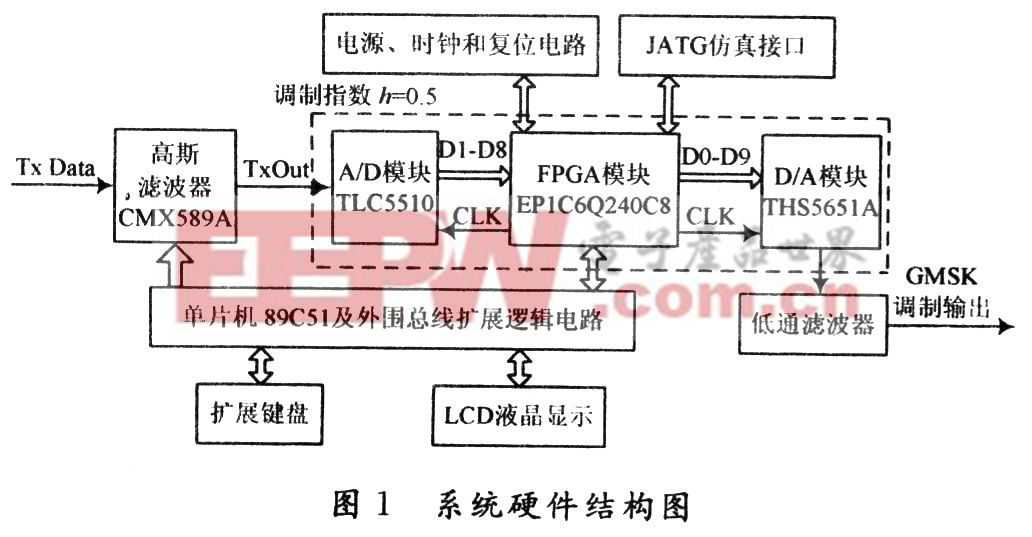

- 摘 要:GMSK信号具有很好的频谱和功率特性,特别适用于功率受限和信道存在非线性、衰落以及多普勒频移的移动突发通信系统。根据GMSK调制的特点,提出亍一种以FPGA和CMX589A为硬件裁体的GMSK调制器的设计方案,并给出

- 关键字:

设计 实现 调制器 GMSK FPGA CMX589A 基于

fpga-nios介绍

您好,目前还没有人创建词条fpga-nios!

欢迎您创建该词条,阐述对fpga-nios的理解,并与今后在此搜索fpga-nios的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473