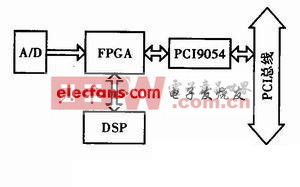

- 本文设计的系统采用PLX公司生产的CPCI协议转换芯片PCI9054,通过Verilog HDL语言在FPGA中产生相应的控制信号,完成对数据的快速读写,从而实现了与CPCI总线的高速数据通信。高速数据传输技术是现代信息技术的前沿科技

- 关键字:

数据通信 CPCI 实现 FPGA 基于

- 摘要:以ADS8341为例,介绍了基于FPGA使用串行输出A/D转换器实现对多通道准同步采样的方法,逻辑控制方式FPGA相比程序流程式的单片机而言,运行更为可靠,通过时序仿真和试验验证了该控制方法的正确性,系统体积小、

- 关键字:

记录仪 应用 数据 微型 FPGA 串行

- 摘要:根据工业应用的实际需要以及网络通信发展的功能要求,提出了基于FPGA智能变送器控制系统的总体方案,设计了以XILINX公司的Spartan3系列XC3S4005PO208C可编程逻辑器件为主控制器、DM9000A为以太网通信接口、SJA

- 关键字:

FPGA 智能变送器

- 该便携式接触网故障信号分析仪采用图形化程序设计语言LabVIEW开发设计, 可实现数据的高速实时采集、在线分析、自动存储、显示等功能。高速数字化仪NI PXI- 5112卡采样速度高、性能稳定可靠, 适宜对高速变化信号的实时监测。将软件安装在PXI- 1042工控机上, 具有体积小、抗干扰能力强、携带方便等特点, 同时具有故障性质判断、故障定位功能。该系统目前已经在石家庄变电所现场运行, 效果良好。

- 关键字:

FPGA 8051 TCP IP

- 摘要 在分析Sony公司ICX098BQ面阵CCD图像传感器驱动时序的基础上,对可调节曝光时间的CCD时序发生器及其硬件电路进行设计。选用FPGA器件作为硬件设计平台,使用VHDL语言对时序关系进行了硬件描述。采用QuartusII 8.0

- 关键字:

FPGA CCD 面阵 发生器

- 随着通信与网络技术的不断发展,使我国用现有的E1资源来传输以太网业务成为广泛的应用。以太网数据要通过E1线路传输就必须对以太网净荷数据进行帧封装,才能从E1线路上恢复出以太网数据帧,完成以太网数据的交换。通常,以太网数据是通过HDLC协议或GFP协议来进行封装的。本文介绍了中国移动标准协议转换器中以太网到单路E1转换器HDLC协议封装的FPGA(现场可编程逻辑阵列)设计与实现。

- 关键字:

中国移动 FPGA 201106

- 摘要 基于Flash存储器的Hamming编码原理,在Altera QuartusⅡ7.0开发环境下,实现ECC校验功能。测试结果表明,该程序可实现每256 Byte数据生成3 Byte的ECC校验数据,能够检测出1 bit错误和2 bit错误,对于1 bit错误

- 关键字:

Flash FPGA NAND ECC

- 随着半导体工艺技术的迅猛发展,现场可编程逻辑器件FPGA的集成度迅速提高,已达到百万门量级,与此同时,FPGA中的逻 ...

- 关键字:

ARM FPGA 加载配置

- 摘要:提出一种通过两个二阶节级联构成四阶IIR数字椭圆滤波器的设计方法,并利用Matlab仿真软件设计了通带内波纹不大于0.1 dB,阻带衰减不小于42 dB的IIR数字滤波器。论述了一种采用可编程逻辑器件,通过VHDL硬件描

- 关键字:

Matlab FPGA IIR 数字滤波器

- 在现代数字通信中,对数据传输容量和传输效率的要求越来越高,因此经常依据时分复用[1]的原理通过数字复接与分...

- 关键字:

数字复接技术 FPGA 时分复用

- 摘要:在FPGA设计中,为了成功地操作,可靠的时钟是非常关键的。设计不良的时钟在极限的温度、电压下将导致错误的行为。在设计PLD/FPGA时通常采用如下四种类型时钟:全局时钟、门控时钟、多级逻辑时钟和波动式时钟。

- 关键字:

FPGA 时钟设计

- 1 引 言 在雷达及声纳信号处理系统中,波束形成算法通常采用DSP软件编程实现,控制逻辑电路采用CPLD来完成,这种方法具有软件编程灵活、功能易于扩展的优点,但对于实时性能要求很高的系统,如雷达、声纳探测和

- 关键字:

FPGA 自适应波束 算法

- 针对高清图像在中值滤波预处理过程中排序量多、速度慢的特点,提出适合邻域图像并行处理机的分块存储方法。在流水线结构下,1个时钟周期可以并行处理32个3×3邻域的中值滤波运算,实现了高速、实时的1 920×1 080灰度图像中值滤波器。

- 关键字:

FPGA 中值滤波 硬件实现

- 莱迪思半导体公司日前宣布LatticeECP3TMFPGA系列符合PCI Express 2.0在2.5Gbps的规范。针对最近PCI – SIG研讨会上涉及的1-通道和 4-通道配置,LatticeECP3 FPGA和其PCI Express(PCIe)IP核通过了符合PCI - SIGPCIe 2.0规范和互操作性的测试,确保莱迪思的解决方案与现有的支持系统的PCIe 2.0具有互操作性。

- 关键字:

莱迪思 FPGA

- 全球可编程平台领导厂商赛灵思公司(Xilinx, Inc. (NASDAQ:XLNX))今天宣布荣膺中国经济CEO论坛“2011中国经济-最佳推动力企业”奖。赛灵思公司全球高级副总裁、亚太地区执行总裁汤立人(Vincent Tong)和亚太地区销售与市场副总裁杨飞先生,出席了由东方企业家、经理人杂志、新民周刊、金融界、北京电视台、香港科技大学商学院、中国企业国际发展协会联合在北京发起主办的 “中国经济CEO论坛暨中国经济成就奖评选颁奖盛典”。 商务部国际贸易经济合作研究院研究员白明代表中国经济CEO 论坛

- 关键字:

赛灵思 FPGA

fpga-1c6介绍

您好,目前还没有人创建词条fpga-1c6!

欢迎您创建该词条,阐述对fpga-1c6的理解,并与今后在此搜索fpga-1c6的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473