- 提出一种基于FPGA的实时视频信号处理平台的设计方法,该系统接收低帧率数字YCbCr视频信号,对接收的视频信号进行格式和彩色空间转换、像素和,利用片外SDRAM存储器作为帧缓存且通过时序控制器进行帧率提高,最后通过VGA控制模块对图像信号进行像素放大并在VGA显示器上实时显示。整个设计使用Verilog HDL语言实现,采用Altera公司的EP2S60F1020C3N芯片作为核心器件并对功能进行了验证。

- 关键字:

FPGA 实时视频 信号处理平台

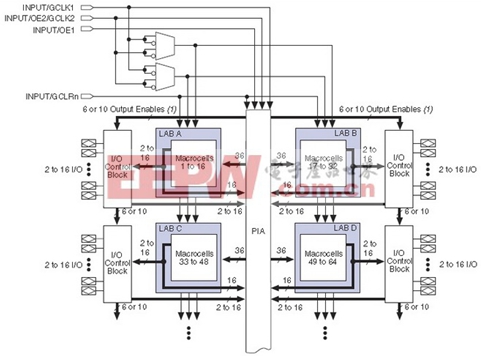

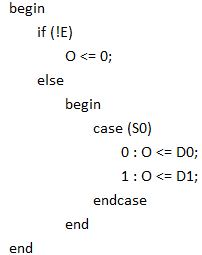

- CPLD和FPGA都是我们经常会用到的器件。有的说有配置芯片的是FPGA,没有的是CPLD;有的说逻辑资源多的是FPGA,少的是CPLD;有的直接就不做区分,把他们都叫做FPGA。那么两者到底有什么区别呢?下面我们就以Altera公司的CPLD和FPGA为例来说说两者的区别。

- 关键字:

CPLD FPGA 逻辑阵列 LAB单元 Altera Xilinx

- 高速SDRAM存储器接口电路设计SDRAM可作为软嵌入式系统的(NIOS II)的程序运行空间,或者作为大量数据的缓冲区。SDRAM是通用的存储设备,只要容量和数据位宽相同,不同公司生产的芯片都是兼容的。一般比较常用的SDRAM

- 关键字:

SDRAM FPGA 最小系统 电路分析

- 下载配置与调试接口电路设计FPGA是SRAM型结构,本身并不能固化程序。因此FPGA需要一片Flash结构的配置芯片来存储逻辑配置信息,用于进行上电配置。以Altera公司的FPGA为例,配置芯片分为串行(EPCSx系列)和并行(EPCx系

- 关键字:

FPGA 最小系统 电路分析 下载

- FPGA管脚设计FPGA的管脚主要包括:用户I/O(User I/O)、配置管脚、电源、时钟及特殊应用管脚等。其中有些管脚可有多种用途,所以在设计FPGA电路之前,需要认真的阅读相应FPGA的芯片手册。下面以Altera公司的Cyclone系

- 关键字:

FPGA 最小系统 电路分析 管脚

- FPGA最小系统是可以使FPGA正常工作的最简单的系统。它的外围电路尽量最少,只包括FPGA必要的控制电路。一般所说的FPGA的最小系统主要包括:FPGA芯片、下载电路、外部时钟、复位电路和电源。如果需要使用NIOS II软嵌

- 关键字:

FPGA 最小系统 概念

- 1.1 FPGA技术的发展历史和动向1.1.1 FPGA技术的发展历史纵观数字集成电路的发展历史,经历了从电子管、晶体管、小规模集成电路到大规模以及超大规模集成电路等不同的阶段。发展到现在,主要有3类电子器件:存储器、

- 关键字:

FPGA 发展

- 从大学时代第一次接触FPGA至今已有10多年的时间。至今记得当初第一次在EDA实验平台上完成数字秒表,抢答器,密码锁等实验时,那个兴奋劲。当时由于没有接触到HDL硬件描述语言,设计都是在MAX+plus II原理图环境下用74系列逻辑器件搭建起来的。

- 关键字:

FPGA EDA VHDL Verilog 时钟 IP核

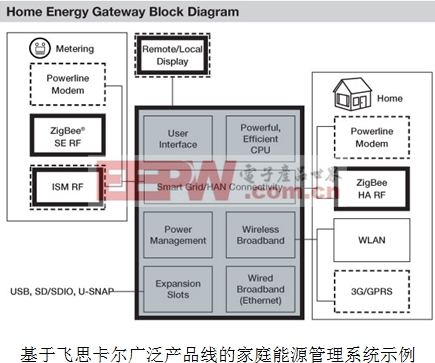

- 智能家居是一个居住环境,是以住宅为平台,装有智能家居的场所。这个场所融合了自动化控制系统、计算机网络系统和网络通信技术的网络化、智能化的家居控制系统。智能家居将让用户有更方便的手段来管理家庭设备,比如,通过触摸屏、互联网或者语音识别控制家用设备,更可以执行场景操作。

- 关键字:

飞思卡尔 MCU 智能家居 物联网 云计算 201310

- DSP是嵌入式开发处理器的三大巨头之一,很多刚刚接触DSP的朋友大都会有这些疑问,为什么要用DSP?DSP是什么、能干嘛?有没有前途,或者有没有“钱途”?好不好学?该怎么学?今天就和大家聊下学习DSP得知道的那些事儿。

- 关键字:

DSP 嵌入式 MCU CPU 单片机

fpga+mpu+mcu介绍

您好,目前还没有人创建词条fpga+mpu+mcu!

欢迎您创建该词条,阐述对fpga+mpu+mcu的理解,并与今后在此搜索fpga+mpu+mcu的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473