- 致力于提供功率管理、安全、可靠与高性能半导体技术产品的领先供应商美高森美公司(Microsemi Corporation,纽约纳斯达克交易所代号:MSCC)为其抗辐射(radiation-hardened)解决方案产品组合增添两款用于航天、商业航空和国防应用的全新超低压降(Ultra-low dropout, ULDO)线性负载点(POL)调节器。

- 关键字:

美高森美 FPGA

- 滤波器是任何信号处理系统的关键组成部分,随着现代应用的日趋复杂,滤波器设计的复杂程度也日益提高。采用 FPGA 设计和实现的高性能滤波器的能力是模拟方法所望尘莫及的。另外,采用FPGA 设计的数字滤波器可以避免模

- 关键字:

FPGA 数字信号处理 滤波器

- 数字硬盘录像机是一种性价比很高的视频监控解决方案,具有对图像/语音进行长时间录像、录音、远程监控和控制...

- 关键字:

DSP FPGA 视频编码器

- 演示程序

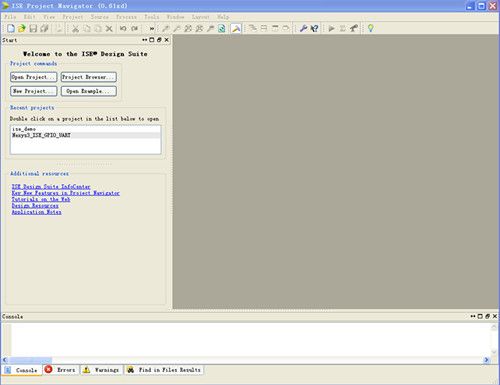

设计工具对于选择FPGA进行设计是非常重要的一个部分,Xilinx公司提供了强大的集成设计工具ISE Design Suite。Spartan-6系列FPGA芯片也是适用于Xilinx所倡导的目标设计平台,丰富的IP资源是设计变得更加灵活、方便。Digilent也提供了丰富的Demo程序和参考设计,可以在其官网免费下载。

本文的演示程序分为两种版本,分别基于ISE和EDK。可以了解如何在ISE环境下进行FPGA的设计以及如何用EDK搭建系统平台。该演示程序主要是如何控制N

- 关键字:

Digilent FPGA

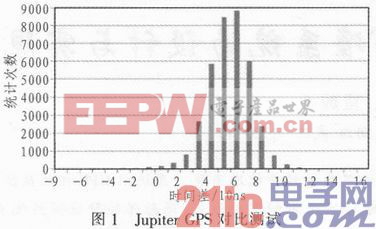

- 针对目前广泛对高精度频率源的需求,利用FPGA设计一种恒温晶振频率校准系统。系统以GPS接收机提供的秒脉冲信号为基准源,通过结合高精度恒温晶振短期稳定度高与GPS长期稳定特性好、跟踪保持特性强的优点,设计数字锁相环调控恒温晶振的频率。详细阐述系统的设计原理及方法,测试结果表明,恒温晶振的频率可快速被校准到10 MHz,频率偏差小于0.01Hz,具有良好的长期稳定性,适合在多领域中作为时间频率的标准。

- 关键字:

频率校准 恒温晶振 数字锁相环 FPGA

- 根据研调机构iSuppli统计资料,2012年MCU全球市场排名中,车用电子大厂瑞萨(Renesas)以4.05亿美元稳坐MCU市场第一名宝座,飞思卡尔(Freescale)则以2.34亿美元位居第二,至于以8位元MCU为主的MicroChip,2012年营收达2.10亿元,名列第三,意法半导体MCU营收则达1.32亿美元,晋升全球第四大MCU厂,而触控厂爱特梅尔(Atmel)则列居第五位,营收达到1.20亿美元。

而英飞凌(Infineon)、恩智浦(NXP)、德州仪器(TI)、东芝(Tosh

- 关键字:

Freescale MCU

- 在Altera宣布进入采用英特尔的14奈米三闸极电晶体制程后,赛灵思(Xilinx)也不甘示弱,宣布进入全新的产品线进入台积电(TSMC)20奈米的投片时程,并于今年第四季取得少量样本,明年第一季正式进入量产时程。

然而,同样也是采取台积电的20奈米制程,Altera旗下的Arria10FPGA,则是在2014年初提供样本贩售,单以台积电的20奈米制程的进度上来说,Altera落后赛灵思约有一季的时间。但相对的,Altera在14奈米三闸极电晶体制程,向英特尔靠拢,将于今年提供测试晶片。就这方面

- 关键字:

Altera FPGA

- 一.面积与速度的平衡互换原则

这里的面积指的是FPGA的芯片资源,包括逻辑资源和I/O资源等;这里的速度指的是FPGA工作的最高频率(和DSP或者ARM不同,FPGA设计的工作频率是不固定的,而是和设计本身的延迟紧密相连)。 在实际设计中,使用最小的面积设计出最高的速度是每一个开发者追求的目标,但是“鱼和熊掌不可兼得”,取舍之间展示了一个开发者的智慧。

1.速度换面积

速度优势可以换取面积的节约。面积越小,就意味着可以用更低的成本来实现产品的功能。速度换面积的

- 关键字:

FPGA DSP

fpga+mpu+mcu介绍

您好,目前还没有人创建词条fpga+mpu+mcu!

欢迎您创建该词条,阐述对fpga+mpu+mcu的理解,并与今后在此搜索fpga+mpu+mcu的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473