- 目前,包括移动设备在内的很多多媒体设备上都使用了摄像头,而且还在以很快的速度更新换代。目前使用的摄像头分为两种:CCD(Charge Couple Device电荷偶合器件)和 CMOS(Complementary Metal Oxide Semiconductor互补

- 关键字:

Sensor CMOS 调试 经验

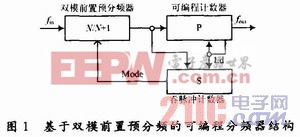

- 1 引言 集成电路是采用半导体制作工艺,在一块较小的单晶硅片上制作上许多晶体管及电阻器、电容器等元器件,并按照多层布线或遂道布线的方法将元器件组合成完整的电子电路。 一个典型的数字锁相环结构如图1 所示

- 关键字:

设计 振荡器 CMOS

- 制定行业公认的标准是研究纳米技术必不可少的先期工作

就像1849年出现的加利福尼亚淘金热一样,纳米技术的出现也带来了巨大机遇和极大风险。正如在淘金热时代出现了很多新技术、利益和挑战一样,人们对纳米技术的探索也将不可避免地促使人们开发一些新工具突破纳米关键技术,抓住创造巨大财

富的机遇,但是也存在给环境、健康和安全带来灾难性影响的可能性。尽管纳米技术将毋庸置疑地形成很多爆炸性的技术,催生很多新的研究领域,但是也可能对那些不了解

- 关键字:

纳米 CMOS

- 本文介绍了电荷俘获的原理以及直流特征分析技术对俘获电荷进行定量分析的局限性。接下来,本文介绍了一种超快的脉冲I-V分析技术,能够对具有快速瞬态充电效应(FTCE)的高k栅晶体管的本征(无俘获)性能进行特征分析。

先进CMOS器件高k栅技术的进展

近年来,高介电常数(高k)材料,例如铪氧化物(HfO2)、锆氧化物(ZrO2)、氧化铝(Al2O3)以及

- 关键字:

脉冲 CMOS

- SuVolta日前宣布推出PowerShrink™低功耗平台。该平台可以有效降低CMOS集成电路2倍以上的功耗,同时保持性能并提高良率。SuVolta和富士通半导体有限公司(Fujitsu Semiconductor Limited)今天还共同宣布,富士通已获得授权使用SuVolta创新型PowerShrink™低功耗技术。

- 关键字:

SuVolta CMOS

- 6月9日,应用于高能效电子产品的首要高性能硅方案供应商安森美(ON Semiconductor)半导体推出五款超小封装的低压降(LDO) 线性稳压器,强化用于智能手机及其他便携电子应用的现有产品阵容。这些新器件基于互补金属氧化物半导体(CMOS)技术,均能提供150毫安(mA)的输出电流。

NCP4682和NCP4685超低电流稳压器的供电电流仅为典型值1微安(µA),输出电压范围为1.2伏(V)至3.3 V。

- 关键字:

安森美 CMOS NCP4682

- 基准电压源可广泛应用于A/D、D/A转换器、随机动态存储器、闪存以及系统集成芯片中。使用0.18 μm CMOS工艺设计了具有高稳定度、低温漂、低输出电压为0.6 V的CMOS基准电压源。

- 关键字:

设计 电压 基准 CMOS 0.18

- 摘要:设计了一种宽带轨对轨运算放大器,此运算放大器在3.3 V单电源下供电,采用电流镜和尾电流开关控制来实现输入级总跨导的恒定。为了能够处理宽的电平范围和得到足够的放大倍数,采用用折叠式共源共栅结构作为前

- 关键字:

CMOS 运算放大器

- 提出一种应用于射频频率合成器的宽分频比可编程分频器设计。该分频器采用脉冲吞吐结构,可编程计数器和吞脉冲计数器都采用改进的CMOS源极耦合(SCL)逻辑结构的模拟电路实现,相对于采用数字电路实现降低了电路的噪声和减少了版图面积。同时,对可编程分频器中的检测和置数逻辑做了改进,提高分频器的工作频率及稳定性。最后,采用TSMC的0.13/μm CMOS工艺,利用Cadence Spectre工具进行仿真,在4.5 GHz频率下,该分频器可实现200~515的分频比,整个功耗不超过19 mW,版图面积为106 μ

- 关键字:

可编程 设计 CMOS 合成器 频率 应用

- 以网络摄像机为应用背景,阐述了数字CMOS图像传感器OV7720芯片的参数、接口和通信协议,结合网络摄像机的开发环境,详细介绍了芯片与嵌入式CPU的硬件电路和软件结构。系统以嵌入式Linux作为操作系统,相机芯片OV7720,OV529对数字视频进行采集、压缩编码并生成MPEG-4码流。MPEG-4码流经过AT91SAM7X256控制器外挂的网络芯片被输送到PC机。PC机端通过内嵌MPEG-4解压插件的IE浏览器实时浏览视频和控制网络摄像机的状态。

- 关键字:

网络 摄像机 设计 OV7720 传感器 CMOS 图像 基于

- 摘要:为解决PWM控制器中输出电压与基准电压的误差放大问题,设计了一款高增益、宽带宽、静态电流小的新型误差放大器,通过在二级放大器中间增加一级缓冲电路,克服补偿电容的前馈效应,同时消除补偿电容引入的零点。

- 关键字:

CMOS PWM 误差放大器

flir cmos介绍

您好,目前还没有人创建词条flir cmos!

欢迎您创建该词条,阐述对flir cmos的理解,并与今后在此搜索flir cmos的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473