- 摘要:以Xilinx的FPGA为例,介绍了FPGA开发系统的电源要求和功耗,并给出了采用线性低压降(LDO)稳压器,DC/DC调整器,DC/DC控制器和电源模块等几种电源解决方案。 关键词:现场可编程门阵列;电源设计;DC/DC变换器

- 关键字:

系统 电源 设计 研究 开发 FPGA 现场 可编程 阵列 大规模

- 美国国家仪器有限公司(National Instruments,简称NI)近日发布了全新NI LabWindows/CVI 2010,该软件可基于验证过的ANSI C测试测量软件平台,提供更高的开发效率,并简化FPGA通信的复杂度。此外,NI还发布了LaWindows/CVI 2010 Linux Run-Time模块和LabWindows/CVI 2010实时模块,可扩展开发环境至Linux和实时操作系统中。

- 关键字:

NI FPGA

- 低功耗和高带宽是下一代高端设计的两个主要需求。对全球范围多个应用领域的调研表明,以相同甚至更低功耗及成本来实现更大的带宽已成为大势所趋。现在应对带宽不断增长的技术是演进中的40G和100G系统(以及即将出现的400G系统)。设计下一代FPGA来满足目前对宽带和低功耗需求的难度越来越大。

- 关键字:

Altera FPGA

- 摘要:提出了一种基于FPGA并利用Verilog HDL实现的CMI编码设计方法。研究了CMI码型的编码特点,提出了利用Altera公司CycloneⅡ系列EP2C5Q型号FPGA完成CMI编码功能的方案。在系统程序设计中,首先产生m序列,然后程序

- 关键字:

FPGA CMI 编码 系统设计

- 摘要:利用FPGA实现时分多址的方法有很多种,但大多数方法都对FPGA芯片资源的占用非常巨大。针对这一问题,提出一种改进型方法来实现时分多址。通过使用FPGA芯片内部的双口随机访问存储器(双口RAM),利用同一块RAM采

- 关键字:

FPGA 时分 多址 改进型

- 摘要:基于FPGA和USB2.0的技术方案,设计了一种高速化和集成化的数据采集系统。该系统是以Altera公司的FPGA芯片EP2C5T144为主控芯片,以Cypress公司的EZ-USB FX2芯片为传输手段设计实现的。首先详细介绍了整体系统的

- 关键字:

FPGA 数据采集系统

- 摘要:激光雷达的发射波及回波信号经光电器件转换形成的电信号具有脉宽窄,幅度低,背景噪声大等特点,对其进行低速数据采集存在数据精度不高等问题。同时,A/D转换器与数字信号处理器直接连接会导致数据传输不

- 关键字:

FPGA DSP 雷达 高速数据

- 摘要:为了提高系统的集成度和可靠性,降低功耗和成本,增强系统的灵活性,提出一种采用非常高速积体电路的硬件描述语言(VHDL语言)来设计数字基带传输系统的方法。详细阐述数字基带传输系统中信号码型的设计原则,数

- 关键字:

FPGA 数字基带 传输系统

- 市场分析师预测,全球营收排名第二大的可程序化逻辑组件供货商Altera,有机会在2012年初取代该市场龙头Xilinx跃上第一大供货商位置。

- 关键字:

Altera FPGA

- 为达到IRIG-B码与时间信号输入、输出的精确同步,采用现代化靶场的IRIG-B码编码和解码的原理,从工程的角度出发,提出了使用现场可编程门阵列(FPGA)来实现IRIG-B码编码和解码的设计方案和体系结构,设计中会涉及到几个不同的时钟频率,FPGA对时钟的同步性具有灵活性、效率高、且功耗低。抗干扰性好的特点。结果表明,FPGA能够确保为从设备提供同源的时钟基准,使时钟与信号的延迟控制在200 ns以内,从而得到了IRIG-B码与时间精确同步的效果。

- 关键字:

IRIG-B FPGA DC 编码

- 激光雷达的发射波及回波信号经光电器件转换形成的电信号具有脉宽窄,幅度低,背景噪声大等特点,对其进行低速数据采集存在数据精度不高等问题。同时,A/D转换器与数字信号处理器直接连接会导致数据传输不及时,影响系统可靠性、实时性。针对激光雷达回拨信号,提出基于FPGA与DSP的高速数据采集系统,利用FPGA内部的异步FIFO和DCM实现A/D转换器与DSP的高速外部存储接口(EMIF)之间的数据传输。介绍了ADC外围电路、工作时序以及DSP的EMIF的设置参数,并对异步FIFO数据读写进行仿真,结合硬件结构详细地

- 关键字:

FPGA DSP 雷达 高速数据

- 为进行高精度信号源的设计,同时降低设计成本,以Cyclone II系列低端FPGA为核心,利用直接频率合成技术,对正弦信号等数据进行1/4周期压缩存储到ROM中,在外部时钟频率为50 MHz,实现了正弦信号源的设计,同时,实现三角波、锯齿波、矩形脉冲及2-ASK、2-PSK和2-FSK等数字调制信号,系统还具有扫频、指定波形次数等功能。仿真结果表明,信号源精度高,频率调整步进可达0.034 92 Hz,频率范围为0.034 92 Hz~9.375 MHz,制作成本低,功能丰富。

- 关键字:

DDFS FPGA 高精度 信号源

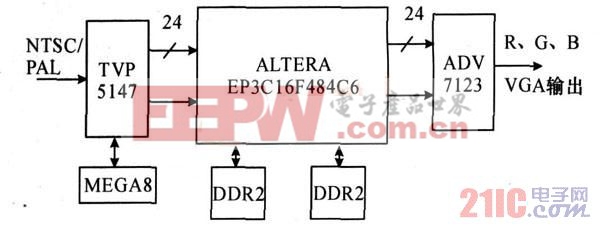

- 摘 要: 针对电视制式PAL /NTSC 信号输出VGA 显示格式的解决办法,详细讲述了基于FPGA 视频格式转换系统的设计实现。采用Cyclone Ⅲ系列的EP3C1*84C6作为核心处理器件,实现了NTSC /PAL制式视频的解码、色空间转换(

- 关键字:

系统 设计 转换 格式 FPGA 视频 基于

- 摘 要:文章中提出了一种应用于FPGA 的嵌入式可配置双端口的块存储器。该存储器包括与其他电路的布线接口、可配置逻辑、可配置译码、高速读写电路。在编程状态下,可对所有存储单元进行清零,且编程后为两端口独

- 关键字:

FPGA SRAM 嵌入式

- 1 设计要求 设计并制作一个数字化语音存储与回放系统,其示意图如图1所示。

图1 数字化语音存储与回放系统示意图 (1)放大器1的增益为46dB,放大器2的增益为40dB,增益均可调; (2)带通滤波器:通带为30

- 关键字:

FPGA 语音存储 回放 系统设计

flash fpga介绍

您好,目前还没有人创建词条flash fpga!

欢迎您创建该词条,阐述对flash fpga的理解,并与今后在此搜索flash fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473