- 8月中旬,由赛灵思公司(Xilinx)主导的“OpenHW2014开源硬件与嵌入式计算大赛”在古城西安完美落幕。决赛入围的19支团队进行了激烈的角逐,最终来自重庆大学的“随身拍智能旋翼飞行器”项目队伍成功夺冠。在之前的预赛中,来自天津大学、中科院、华中科技大学的团队分别荣获HLS挑战赛专项一等奖。

赛灵思公司全球大学计划总监Patrick Lysaght表示:“我们非常高兴地看到越来越多的高校和知名企业加入到赛灵思率先发起的开源硬件事业

- 关键字:

赛灵思 嵌入式 FPGA 201409

- Altera公司今天宣布,获得富士施乐有限公司2014年度优秀合作伙伴奖。富士施乐公司总部位于日本,在亚太地区开发、生产并销售静电复印(或者电子照相复印)以及文档相关产品和服务。这是Altera连续第二年获得富士施乐公司的优秀合作伙伴奖,Altera FPGA和SoC可编程逻辑器件和技术以其优异的技术、极高的性价比和出众的交付能力而再次获得这一最高荣誉。

富士施乐有限公司副总裁兼采购部执行总经理Tomoyuki Matsuura评论说:“多年以来,Altera一直为我们的业务提供可靠

- 关键字:

Altera FPGA SoC

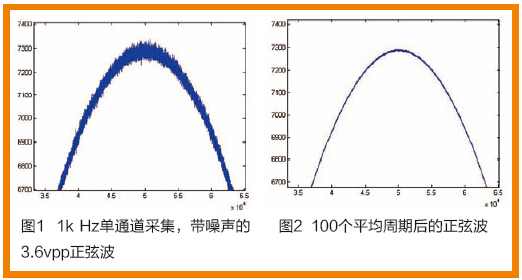

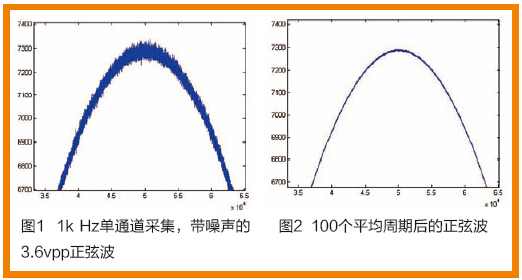

- 许多高速数据采集应用,如激光雷达或光纤测试等,都需要从嘈杂的环境中采集小的重复信号,因此对于数据采集系统的设计来说,最大的挑战就是如何最大限度地减少噪声的影响。利用信号平均技术,可以让您的测量测试系统获取更加可靠的、更加有效的测试数据。

通常情况下,在模拟信号的测试中,所采集到的数据往往夹杂着一些不需要的、随机的内容,这些数据是由周围的干扰或者测试误差所引起的,我们称之为随机噪声,这种噪声可能会影响我们的目标信号,也就是我们需要采集的数据。而采用信号平均技术,则可以减少随机噪声的影响,提升信噪比

- 关键字:

凌华 FPGA DSP PCIe-9852 201409

- 0 引 言

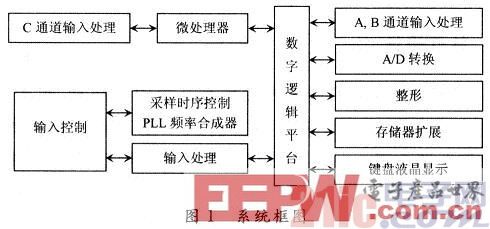

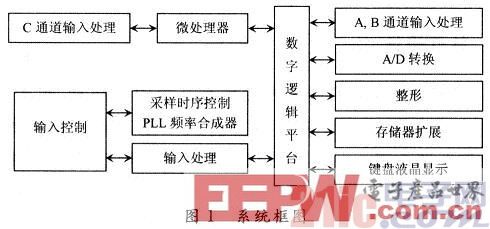

传统的数据采集系统一般采用单片机,系统大多通过PCI总线完成数据的传输。其缺点是数学运算能力差;受限于计算机插槽数量和中断资源;不便于连接与安装;易受机箱内电磁环境的影响。这些问题遏制了基于PCI总线的数据采集系统的进一步开发和应用。因此,需要一种更为简便通用的方式完成采集系统和计算机数据的交互。

数据采集系统性能的好坏,主要取决于它的精度和速度。在保证精度的条件下应尽可能地提高采样速度,以满足实时采集、实时处理和实时控制的要求。实践表明,采用ARM 32位嵌入式微处理器作为控

- 关键字:

FPGA PCI总线 ARM

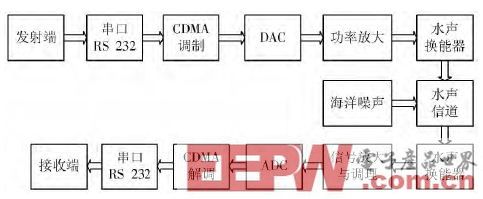

- 任何信息需要借助声、光、电信 号进行传递,由于光信号和电信号在海水中的衰减比较严重,而声波是人类迄今为止已知的惟一能在水中远距离传播的能量形势,因此,近些年海洋中的水声通信系统的研究以及开发成了热点。水声通信是指利用水声信道进行通信双方数据传输的通信系统,水声通信系统构成与传统的无线电通信系统构成具有极大的相似性,但是水声通信系统是将电信号转换成声信号,携载信息的声信号在水中进行传播完成系统的数据传输。

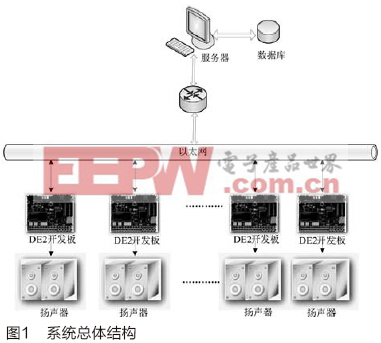

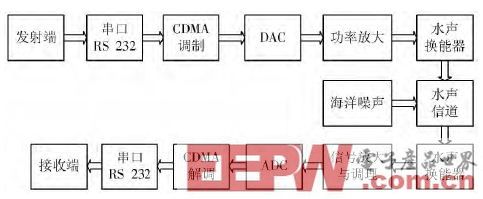

1 水声通信系统的总体结构

基于CDMA的水声通信调制/解调系统的设计框图如图1所示,

- 关键字:

FPGA CDMA ADS7800

- 致力于提供低功耗、安全、可靠与高性能半导体技术方案的领先供应商美高森美公司(Microsemi Corporation) 和技术研发服务领先企业eInfochips宣布共同合作为航空航天工业提供DO-254兼容设计服务。建设关键性航空电子系统的企业现在能够利用美高森美获奖的SmartFusion2®和IGLOO2®等基于FPGA产品的配置翻转免疫能力(immunity to configuration upsets),并且能够依赖eInfochips部署的先进设计实践来提升设计效率、可

- 关键字:

美高森美 eInfochips FPGA

- 看似简单的几个问题,Andrew却回答的井井有条,小编已经没有办法有什么其他词语去形容了。本文Andrew不仅仅对FPGA入门学习流程做了详细的分享,更是对FPGA开发工作的要求分成大公司和小公司两个层面来分析。你能想象曾经从一个疏忽学业的人成为一名资深FAE的嘛?

1. 您认为想学FPGA的话,先学好什么才最重要?

Andrew:我们玩FPGA的通常就是跟数字电路打交道,要想玩得转,必须先学习并掌握最最基础的数字电路和HDL硬件描述语言,当然这只是入门必备,实际上远远不够。个人拙见,要入

- 关键字:

ALTEAR FPGA FAE

- 电流互感器作为高压电网检测主要设备,不仅为电能的计量提供参数,而且是为继电保护提供动作的依据。随着国家智能电网和特高压电网的发展,传统电磁式电流互感器逐渐暴露出其致命缺陷,例如高电压等级时绝缘极为困难、更高电压下易磁饱和导致测量精度下降等。相比之下,光纤电流互感器具有抗电磁干扰能力强、绝缘可靠、测量精度高、结构简单和体积小巧等诸多优点,是当前研究热点。作为光纤电流互感器的核心部件,其检测和控制电路对电流检测精度和范围具有非常重要的影响。

目前检测和控制电路实现主要有两种方案,一种是以数字信号处理

- 关键字:

FPGA DSP 互感器

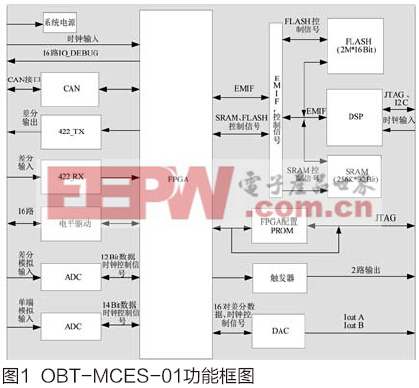

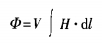

- 对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,提出了提高复位设计可靠性的4种方法,包括清除复位信号上的毛刺、异步复位同步释放、采用专用全局异步复位/置位资源和采用内部复位。上述方法可有效提高FPGA复位的可靠性。

对FPGA芯片而言,在给芯片加电工作前,芯片内部各个节点电位的变化情况均不确定、不可控,而这种不确定且不可控的情况会使芯片在上电后的工作状态出现错误。因此,在FPGA的设计中,为保证系统能可靠进进入工作状态,以及避免对FPGA输

- 关键字:

FPGA 异步复位 异步复位

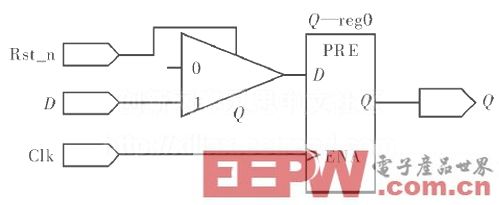

- 0 引言

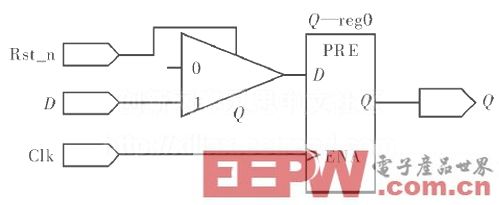

基于SoPC 技术开发的嵌入式Nios Ⅱ软核多处理器系统具有可自主设计,重构性好,软硬件裁剪容易,系统扩充升级方便,能兼顾性能、体积、功耗、成本、可靠性等方面的要求。研发嵌入式Nios Ⅱ软核多处理器系统,是提高嵌入式系统性价比和实用性一种有效途径。

1 片上Nios Ⅱ嵌入式软核多处理器系统

嵌入式系统的核心是RISC 处理器,具有代表性的RISC软核处理器是Nios Ⅱ处理器。软核处理器是指用编程的方法生成的处理器。是一种将硬件逻辑、智能算法、硬件描述语言和编程有机的

- 关键字:

FPGA Nios Ⅱ SoPC

- 致力于提供功耗、安全、可靠与高性能半导体技术方案的领先供应商美高森美公司(Microsemi Corporation) 宣布SmartFusion®2 SoC FPGA和 IGLOO®2 FPGA产品系列是唯一首先成功完成美国国家安全局(NSA)信息安全保障局(IAD)安全实施指南(SIG)文件的FPGA器件。

NSA IAD 设立这一过程,旨为提供与一套信息保障 (IA) 系统使用模型最具相关性的设计和数据安全特性概述,并包括了用于基于合适用户场景的安全条例指南。通过清楚的Sm

- 关键字:

美高森美 FPGA SoC

- TrendForce旗下内存储存事业处DRAMeXchange最新调查显示,由于智能手机、平板电脑等移动装置需求稳健增长,固态硬盘在笔记本电脑以及服务器与数据中心的需求增加,而物联网应用也将逐渐导入NANDFlash,2015年NANDFlash整体产业规模将提升至266亿美元,年增长9%。

DRAMeXchange研究协理杨文得表示,2014年NANDFlash需求位增长率为36%,在更多元化的产品开始导入NANDFlash的挹注下,2015年的需求位增长率将依旧有35%。市场趋势观察的重

- 关键字:

NAND Flash 穿戴性装置

- 致力于提供功耗、安全、可靠与高性能半导体技术方案的领先供应商美高森美公司(Microsemi Corporation) 宣布已从Rambus公司属下Cryptography Research获得其现有差分功率分析(Differential Power Analysis, DPA)专利许可的延期,这项专利许可延期可让美高森美继续使用Cryptography Research专利的突破性DPA对策产品组合,提供业界领先的第三方处理器和FPGA安全启动解决方案。

美高森美是目前拥有使用DPA对策专利许

- 关键字:

美高森美 差分功率分析 FPGA

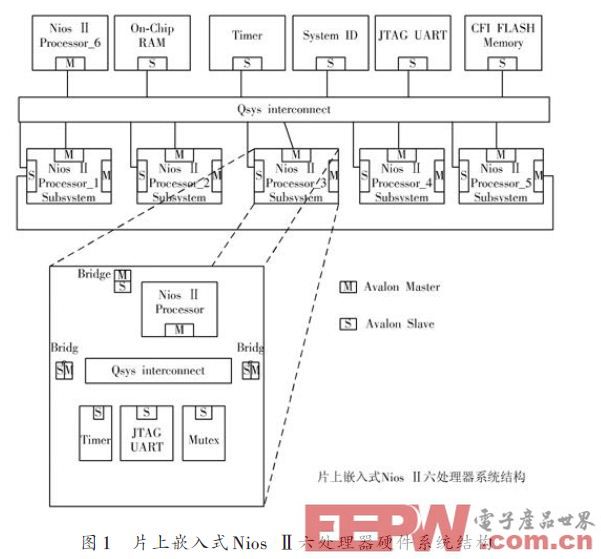

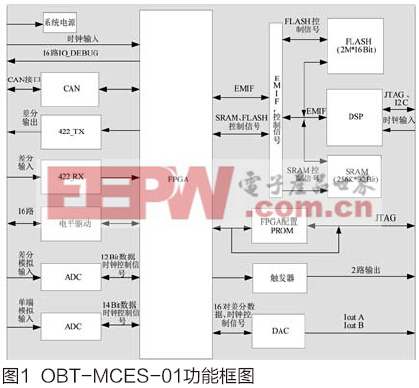

- 摘要:本文在SIP立体封装技术的基础上,设计了基于DSP、FPGA的复合电子系统模块。重点介绍了模块的功能构成及模块接口应用,为基于SIP小型化封装的复合电子系统(功能可订制)提供应用基础。

引言

随着电子技术的发展对系统模块小型化高可靠性提出了更高的要求。复合电子系统模块是欧比特公司推出的一款SIP模块,其将特定(可定制)的电子系统功能模块采用立体封装技术制作而成。本文介绍了基于DSP、FPGA的复合电子系统模块OBT-MCES-01的功能构成以及应用方法。

1 SIP简介

- 关键字:

复合电子系统 DSP FPGA ADC DAC RS422 CAN 201409

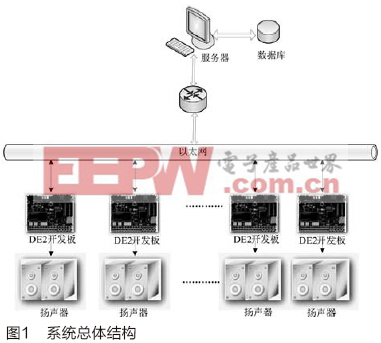

- 摘要:介绍了一种使用Altera DE2开发板以及Qt技术实现的定时音频广播系统。该系统使用C/S架构,使用跨平台Qt技术在Ubuntu系统平台下建立起服务器程序,用于管理所有在线的DE2音频播放终端,使用Sqlite轻量级数据库进行数据存储。通过基于Nios II实现的软核进行外围设备的管理,并播放位于SD卡中的音频文件。

引言

随着数字和网络等技术的发展,广播技术已经呈现出越来越多元化的趋势,其最主要的趋势便是从模拟到数字的转化。从宏观来说,广播技术大体上可以分为三类:传统公共广播系统

- 关键字:

FPGA 扬声器 SD卡 UDP Qt 201409

flash fpga介绍

您好,目前还没有人创建词条flash fpga!

欢迎您创建该词条,阐述对flash fpga的理解,并与今后在此搜索flash fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473