- 为了满足目前对数据处理速度的需求,设计了一种基于FPGA+DDS的控制系统。根据AD9910的特点设计了控制系统的硬件部分,详细阐述了电源、地和滤波器的设计。设计了FPGA的软件控制流程,给出了流程图和关键部分的例程,并对DDS AD9910各个控制寄存器的设置与时序进行详细说明,最后给出了实验结果。实验结果证明输出波形质量高、效果好。对于频率源的设计与实现具有工程实践意义。

- 关键字:

FPGA 9910 AD 控制设计

- 全球可编程逻辑解决方案领先厂商赛灵思公司(NASDAQ:XLNX))今日宣布与全球半导体设计、验证和制造领域的软件及 IP 领先厂商Synopsys公司(NASDAQ:SNPS)联手推出《 FPGA的原型开发方法手册》(FPMM),这是一本介绍如何使用 FPGA 作为平台进行片上系统(SoC)开发的实用指南。FPMM 收录了众多公司的设计团队在设计和验证方面的宝贵经验。

- 关键字:

赛灵思 FPGA

- 摘要:以Xilinx的FPGA为例,介绍了FPGA开发系统的电源要求和功耗,并给出了采用线性低压降(LDO)稳压器,DC/DC调整器,DC/DC控制器和电源模块等几种电源解决方案。 关键词:现场可编程门阵列;电源设计;DC/DC变换器

- 关键字:

系统 电源 设计 研究 开发 FPGA 现场 可编程 阵列 大规模

- 记者3月17日从中国电子科技集团公司38所获悉,由该所自主研发的首个国产化高性能芯片“魂芯一号”,日前在北京“十一五”国家重大科技成就展上首次精彩亮相,其运算能力达每秒钟300亿次浮点运算或每秒钟80亿次浮点乘法累加运算,性能可与国际市场同类产品相媲美,其成功应用将填补我国高性能芯片国产 化的空白。

- 关键字:

DSP 物联网 通讯 魂芯一号

- 美国国家仪器有限公司(National Instruments,简称NI)近日发布了全新NI LabWindows/CVI 2010,该软件可基于验证过的ANSI C测试测量软件平台,提供更高的开发效率,并简化FPGA通信的复杂度。此外,NI还发布了LaWindows/CVI 2010 Linux Run-Time模块和LabWindows/CVI 2010实时模块,可扩展开发环境至Linux和实时操作系统中。

- 关键字:

NI FPGA

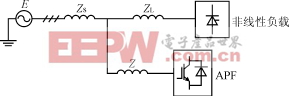

- 基于DSP的滞环跟踪型有源电力滤波器数字控制系统,摘要:介绍了一种基于新型数字信号处理器(DSP)TMS320F2407A数字控制的滞环跟踪型并联有源电力滤波器,以DSP为核心的数字控制电路完成谐波提取、指令电流产生、直流侧电压控制、系统保护等功能,实现了一种全数字控

- 关键字:

滤波器 数字 控制系统 电力 有源 DSP 跟踪 基于

- 基于DSP实现可并机的逆变电源,摘要:介绍了一种可并机的逆变电源的结构和原理,并以Motorola公司的DSP56F805型数字信号处理器作为控制核心,且给出了硬件和软件的设计方案。实验结果证明此系统的控制获得了良好的效果。 关键词:逆变器;并联;数

- 关键字:

逆变电源 实现 DSP 基于

- 低功耗和高带宽是下一代高端设计的两个主要需求。对全球范围多个应用领域的调研表明,以相同甚至更低功耗及成本来实现更大的带宽已成为大势所趋。现在应对带宽不断增长的技术是演进中的40G和100G系统(以及即将出现的400G系统)。设计下一代FPGA来满足目前对宽带和低功耗需求的难度越来越大。

- 关键字:

Altera FPGA

- 摘要:提出了一种基于FPGA并利用Verilog HDL实现的CMI编码设计方法。研究了CMI码型的编码特点,提出了利用Altera公司CycloneⅡ系列EP2C5Q型号FPGA完成CMI编码功能的方案。在系统程序设计中,首先产生m序列,然后程序

- 关键字:

FPGA CMI 编码 系统设计

- 摘要:利用FPGA实现时分多址的方法有很多种,但大多数方法都对FPGA芯片资源的占用非常巨大。针对这一问题,提出一种改进型方法来实现时分多址。通过使用FPGA芯片内部的双口随机访问存储器(双口RAM),利用同一块RAM采

- 关键字:

FPGA 时分 多址 改进型

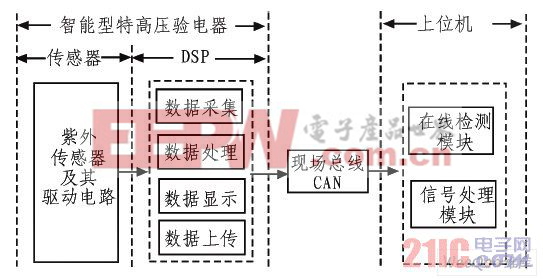

- 基于DSP+LabVIEW的特高压验电器设计方案, 随着电力工业的发展和电网负荷需求的提高,我国正在大力发展特高压、长距离输电技术。高电压导致强电场、电气设备绝缘中的某些薄弱部分在强电场的作用下发生局部放电,同时当架空输电线路表面的电场强度超过空气

- 关键字:

设计 方案 验电器 高压 DSP LabVIEW 基于

- 摘要:基于FPGA和USB2.0的技术方案,设计了一种高速化和集成化的数据采集系统。该系统是以Altera公司的FPGA芯片EP2C5T144为主控芯片,以Cypress公司的EZ-USB FX2芯片为传输手段设计实现的。首先详细介绍了整体系统的

- 关键字:

FPGA 数据采集系统

- 摘要:激光雷达的发射波及回波信号经光电器件转换形成的电信号具有脉宽窄,幅度低,背景噪声大等特点,对其进行低速数据采集存在数据精度不高等问题。同时,A/D转换器与数字信号处理器直接连接会导致数据传输不

- 关键字:

FPGA DSP 雷达 高速数据

- 摘要:为了提高系统的集成度和可靠性,降低功耗和成本,增强系统的灵活性,提出一种采用非常高速积体电路的硬件描述语言(VHDL语言)来设计数字基带传输系统的方法。详细阐述数字基带传输系统中信号码型的设计原则,数

- 关键字:

FPGA 数字基带 传输系统

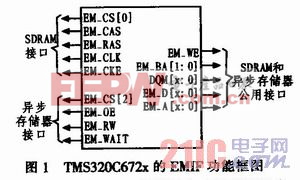

- TMS320C672x系列浮点DSP的EMIF研究与应用,针对如何灵活应用高性能32/64位浮点DSP TMS320C672x提供的性能优良的外部存储器接口(EMIF),分析了EMIF的特点和使用技巧,以TMS320C6722B型DSP为例,设计了EMIF与外部HY57V281620A型SDRAM和异步AM29LV800BB-90EC型Flash的硬件接口,并分析了EMIF访问SDRAM和Flash时各控制寄存器配置的方法和具体步骤,列出了该配置命令下EMIF引脚与逻辑地址的对应关系和具体的软件编写例程;

- 关键字:

研究 应用 EMIF DSP 系列 浮点 TMS320C672x

dsp+fpga介绍

您好,目前还没有人创建词条dsp+fpga!

欢迎您创建该词条,阐述对dsp+fpga的理解,并与今后在此搜索dsp+fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473