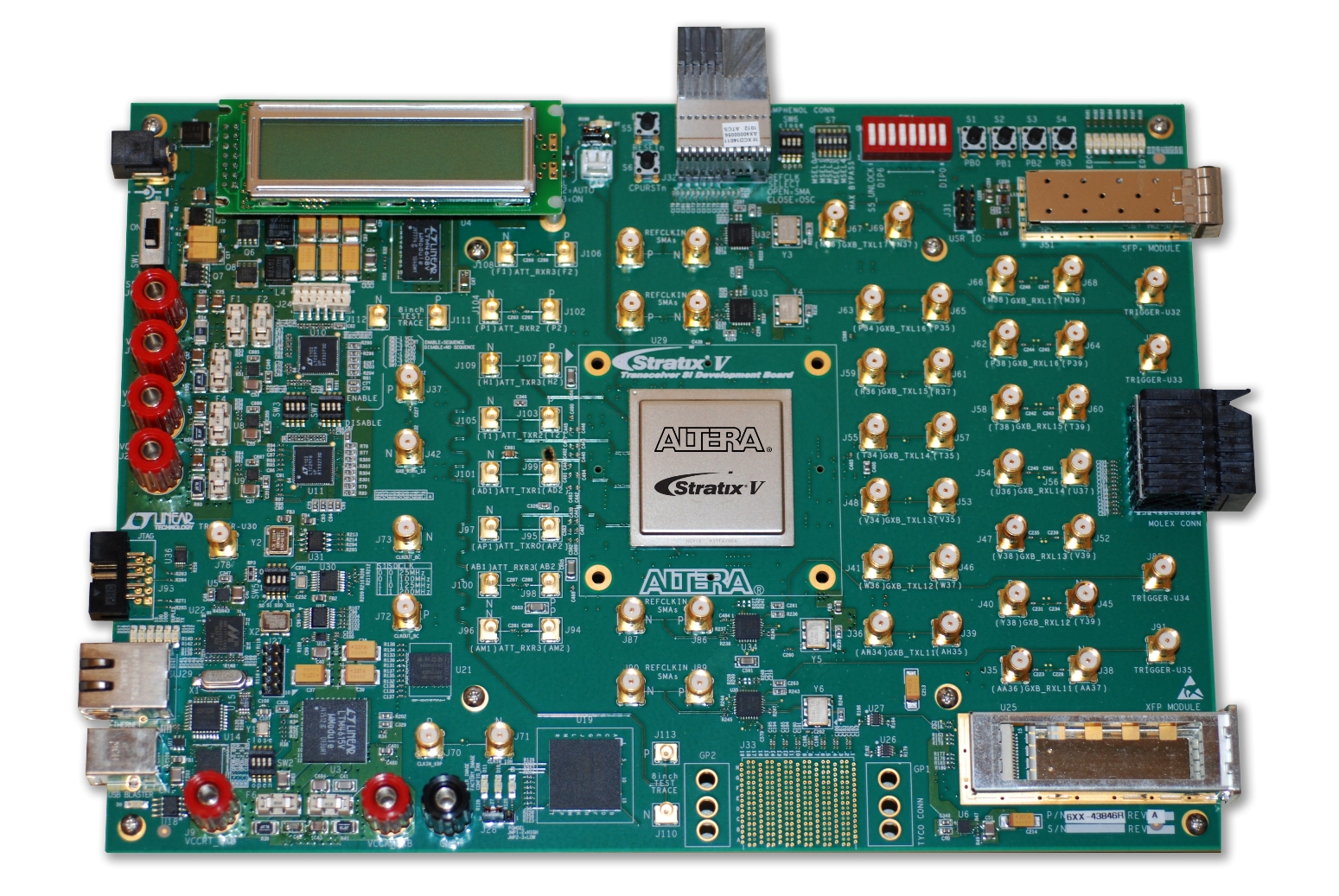

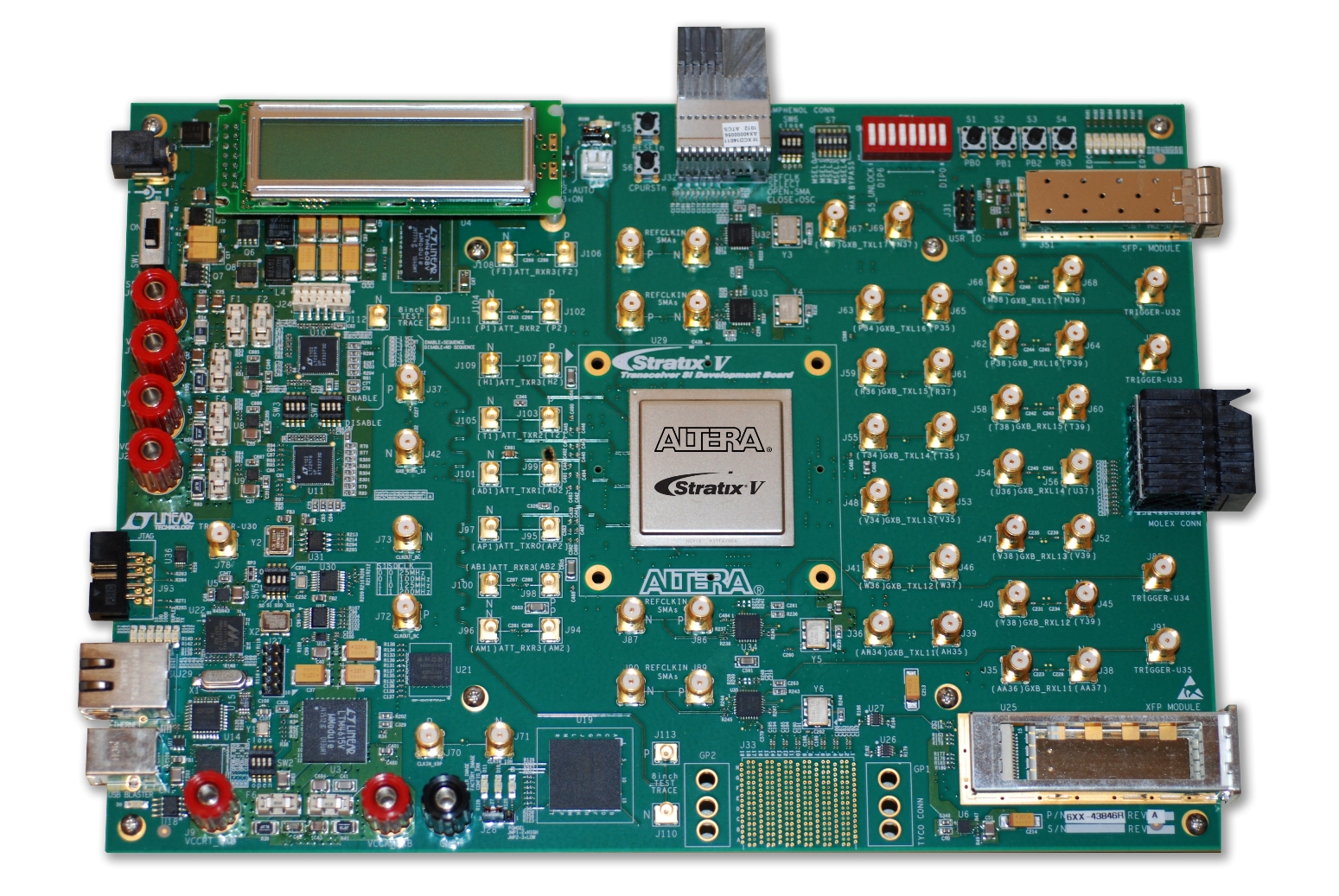

- Altera公司日前宣布开始提供第一款带有28-nm FPGA的开发套件——Stratix V GX FPGA信号完整性套件,在推动业界28-nm FPGA发展方面树立了新里程碑。这一全功能套件支持设计工程师加速高性能系统的设计和开发,满足了业界对提高带宽的需求。Stratix V GX FPGA信号完整性开发套件为用户提供的平台能够测量并评估从600 Mbps到12.5 Gbps的收发器链路性能。

- 关键字:

Altera FPGA

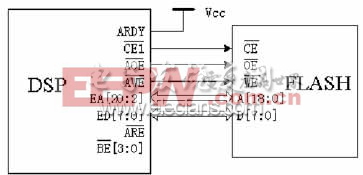

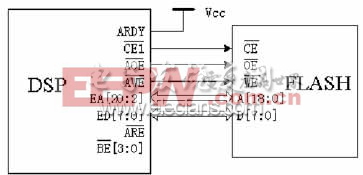

- 基于DSP的外部存储器引导方法实现,TI公司的高速数字信号处理器TMS320C6000系列DSP支持并行处理,采用甚长指令字(VLIW)体系结构,内部设置有8个功能单元(两个乘法器和6个ALU),8个功能单元可并行操作,最多可以在一个周期内同时执行八条32位指令。指令

- 关键字:

方法 实现 引导 存储器 DSP 外部 基于

- 基于FPGA的TMR方法改进策略,基于SRAM的FPGA对于空间粒子辐射非常敏感,很容易产生软故障,所以对基于FPGA的电子系统采取容错措施以防止此类故障的出现是非常重要的。三模冗余(TMR)方法以其实现的简单性和效果的可靠性而被广泛用于对单粒子翻转(

- 关键字:

改进 策略 方法 TMR FPGA 基于

- 2011年9月7号,北京——Altera公司(NASDAQ:ALTR)今天宣布开始提供第一款带有28-nm FPGA的开发套件——Stratix V GX FPGA信号完整性套件,在推动业界28-nm FPGA发展方面树立了新里程碑。这一全功能套件支持设计工程师加速高性能系统的设计和开发,满足了业界对提高带宽的需求。Stratix V GX FPGA信号完整性开发套件为用户提供的平台能够测量并评估从600 Mbps到12.5 Gbps的收发器链路性能。

- 关键字:

Altera FPGA Stratix V GX

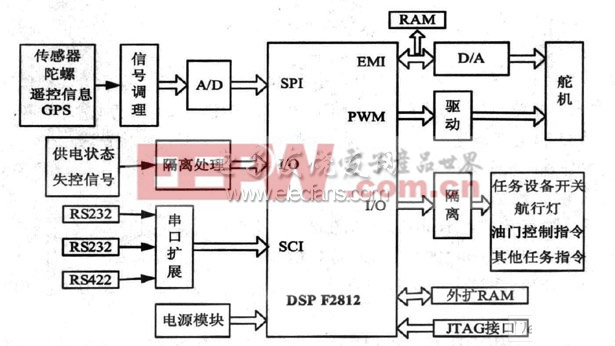

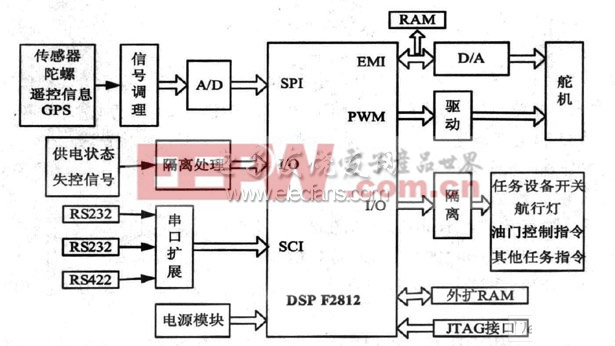

- 1 引 言 本系统选用的TMS320F2812(以下简称F2812)是TI公司开发的一款32 位DSP芯片, 采用高性能静态CMOS 技术, 工作主频可达150M ips。片内集成了128K 字的FLASH 存储器, 方便实现软件升级;还集成了丰富的外围设

- 关键字:

控制系统 飞行器 无人 实现 DSP

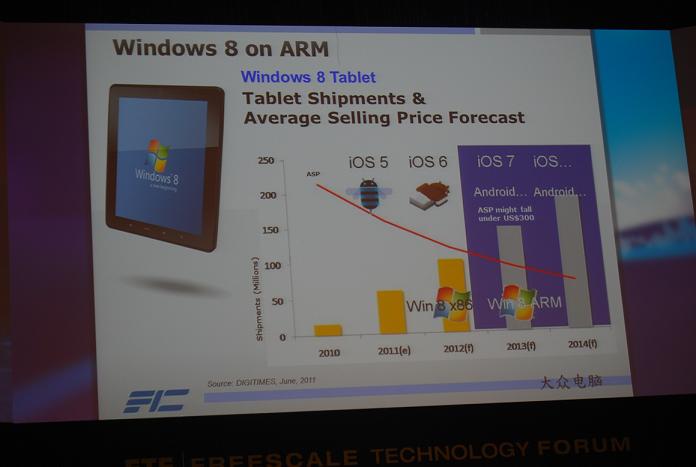

- 在深圳音乐厅举办的飞思卡尔技术论坛(FTF)主题演讲上,让昌旭和在座的千名观众最震撼的可能不是它将推出的多核处理器DSP,而是飞思卡尔CEORichBeyer非常肯定的一句判断:“五年内平板电脑将取代PC的位置。”为了证实他的观点,他还请来台湾大众电脑集团总裁简明仁上台助威。简明仁指出:“虽然现在PC仍是商用的首选,但是不久的将来,平板电脑会成为商用首选。”简明仁特别指出,

- 关键字:

FTF DSP 平板电脑

- 为了继续为设计人员提供低成本、高性能的数字信号处理选择,ADI公司(Analog Devices, Inc.)(NYSE: ADI)推出了ADSP-BF592 Blackfin(R)嵌入式处理器的200-MHz 版本,它以1.99美元/片(千片订量)的价格提供400-MMAC 性能。这款低成本的200 MHz 版本产品的 BDTImark2000性能得分为1120分,BDTImark2000/$ 性价比得分为562分,而400 MHz 版本产品的 BDTImark2000(TM) 得分和 BDTImar

- 关键字:

ADI DSP BDTImark2000

- 2011年8月31日上午8:00整,2011年全国大学生电子设计竞赛(上海赛区TI杯)在上海各参赛学校正式拉开帷幕。今年上海赛区的比赛由上海市教委主办,上海交通大学承办,并继续由全球领先的半导体公司德州仪器(TI)赞助冠名,称为“TI杯”。 2011年上海赛区共有来自19所高校的251支参赛队,753名参赛学生报名参加。

- 关键字:

TI DSP

- 致力于提供帮助功率管理、安全、可靠与高性能半导体技术产品的领先供应商美高森美公司(Microsemi Corporation,纽约纳斯达克交易所代号:MSCC) 宣布提供经成本优化的SmartFusion 可定制单芯片系统 (customizable system-on-chip, cSoC) 器件A2F060,该器件备有商用和工业温度等级型款,专门针对大批量应用而设计,包括马达和运动控制、游戏机、太阳能逆变器,以及临床和成像医疗电子设备。

- 关键字:

美高森美 FPGA

- 日前,飞思卡尔半导体 [NYSE: FSL] 与清华大学签订许可授权协议,这所重点高校将获权使用飞思卡尔e200z6-z3内核;飞思卡尔与中国最高学府的携手合作也将成为推进Power Architecture技术在中国发展步伐的里程碑。同时,清华大学也表示,今后会在飞思卡尔e200内核的基础上研发新产品,并为学生提供Power Architecture技术培训。

- 关键字:

飞思卡尔 半导体 DSP

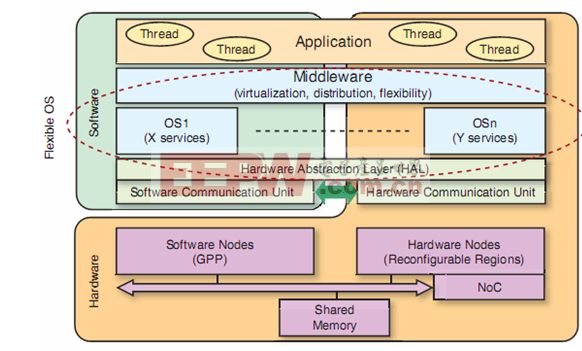

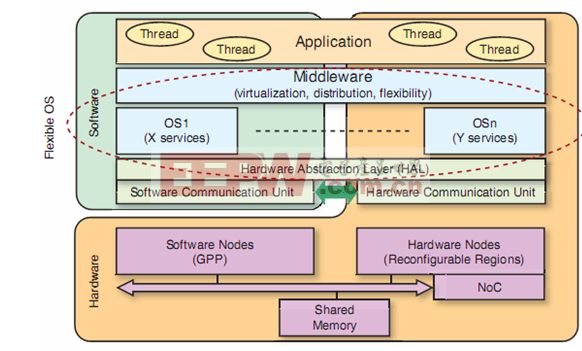

- 利用赛灵思FPGA的动态重配置功能,同构多线程执行模型可同时兼得软件灵活性和硬件性能。一台在未知的土地...

- 关键字:

赛灵思 FPGA

- 本文采用FPGA来设计一款广泛应用于计算机、Modem、数据终端以及许多其他数字设备之间的数据传输的专用异步并行通信接口芯片,实现了某一时钟域(如66 MHz)的8位并行数据到另一低时钟域(如40 MHz)16位并行数据的异步转换,并且客户可以根据自己的要求进行数据定义。完成数据在不同时钟域间的正确传递的同时防止亚稳态的出现,保持系统的稳定,是电路设计的关键。

- 关键字:

Spartan-II FPGA 多时钟域 数据

- 在LMS算法进行变步长处理的基础上,结合驰豫超前流水线技术和时序重构技术提出了创新结构和改进算法,在FPGA的仿真综合环境中设计实现了该高速自适应滤波器,并且在Altera DE2-70开发板上进行了板级测试。

- 关键字:

FPGA 自适应滤波器

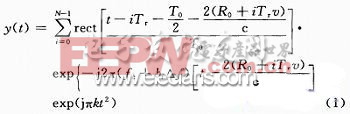

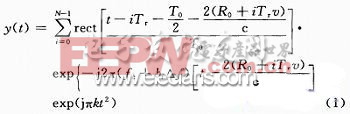

- 基于DSP和FPGA的多波形雷达回波中频模拟器实现,本文论述一种自主产生式的雷达回波模拟器中频部分的设计实现方法,该模拟器可产生脉冲单频、脉冲线性调频、步进频、步进频+线性调频等多种波形的雷达回波信号,并可产生双目标和参数可控的带限高斯白噪声,可模拟主要

- 关键字:

中频 模拟器 实现 雷达 波形 DSP FPGA 基于

- 一台在未知的土地上行进的自动机器人;一部能够根据信号强度改变解压缩格式的视频解码器;一套宽带电子对抗系统;一种用于机动车辆的自适应图像跟踪算法……这些都属于大量涌现的随环境瞬变做出快速响应的新兴嵌入式或者关键任务应用。在过去,静态决策最坏情况分配曾为严格的实时约束提供了解决方案,而现在灵活性也成为一项要求。法国某研究项目建议使用的解决方案是一种分布在 FPGA 资源上,对软硬件线程进行管理的操作系统。

- 关键字:

赛灵思 FPGA

dsp+fpga介绍

您好,目前还没有人创建词条dsp+fpga!

欢迎您创建该词条,阐述对dsp+fpga的理解,并与今后在此搜索dsp+fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473