- ATM可以提供空前的可伸缩性和性价比,以及对将来的实时业务、多媒体业务等的支持,ATM将扮演重要的角色。但目前的信息体系,即LAN和WAN,建立在网络层协议如IP、IPX、AppleTalk等的基础上,因此,ATM的成功及Internet

- 关键字:

技术 介绍 兼容 IP 网络 ATM

- 基于IP复用和SOC技术的微处理器FSPLCSOC模块设计,1 引言 文中采用IP核复用方法和SOC技术基于AVR 8位微处理器AT90S1200IP Core设计专用PLC微处理器FSPLCSOC模块。随着芯片集成程度的飞速提高,IC产业中形成了以片上系统SOC(System-on-Chip)技术为主的设计方式。一

- 关键字:

FSPLCSOC 模块 设计 微处理器 技术 IP 复用 SOC 基于

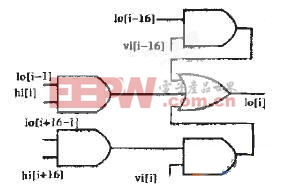

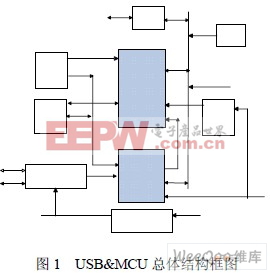

- MCUUSB设备控制器IP核的设计,摘要:用硬件描述语言verilog HDL设计实现了一种MCUUSB设备控制器IP核。论文首先简要介绍了设计的背景,重点对自主研发的将MCUUSB控制器集成于一个芯片的设计和研究分析。最后给出nc-verilog功能仿真方案以及FPGA验

- 关键字:

设计 IP 控制器 设备 MCU&USB

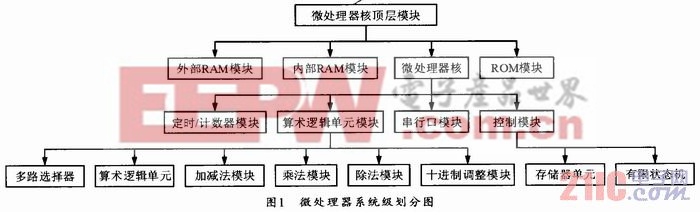

- 嵌入式微处理器IP core设计与分析,摘要:本文在对传统微控制器进行系统分析的基础上,提出了一种较好的改进设计方法。回避了传统微控制器基于累加器的ALU结构及算术逻辑指令:并在指令执行时序上尽量减少指令执行所需的时钟周期。通过仿真验证证明该设

- 关键字:

设计 分析 core IP 微处理器 嵌入式

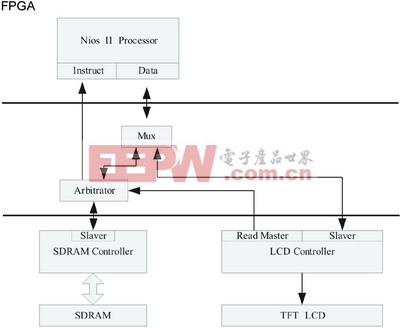

- 系统总体设计方案本系统的总体设计框图如图1所示。

图1 系统框图

Nios II处理器在SDRAM中开辟帧缓冲(Frame buffer),可以是单缓冲也可以是双缓冲。以单缓冲为例。处理器将一帧图像数据(640times;480times;2Byt

- 关键字:

IP 驱动 设计 LCD TFT 嵌入式 Linux 基于

- 1 引言 随着芯片集成程度的飞速提高,一个电子系统或分系统可以完全集成在一个芯片上,IC产业中形成了以片上系统SOC(System-on-Chip)技术为主的设计方式。同时IC设计能力和EDA工具却相对落后于半导体工艺技术的发

- 关键字:

复用 技术 设计 IP AT90S1200 AVR

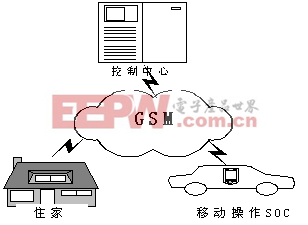

- 移动操作SoC接口IP组件设计, 1 引言

移动操作或移动计算(mobile computing)原是通讯领域的研究方向,随着数字无线通信技术和嵌入式计算技术的发展、应用与融合,移动操作已逐步成为嵌入式系统中很具发展潜力的一个领域[1]。SoC(Sy

- 关键字:

组件 设计 IP 接口 操作 SoC 移动

- 拥有软电话视频许可的用户,只需要在桌面电脑上安装Avaya的IP软件电话,并且配置一个普通的USB摄像头,即具备了端到端视频通信功能。Avaya IP语音通信系统可为使用Avaya IP软件电话的用户提供端到端的视频通信能力。

- 关键字:

视频 通信技术 设计 电话 IP 基于

- 水声信道匹配基础研究是建立在水声学、海洋物理声学以及现代信号处理技术基础上的新兴研究领域。为满足研究需要而构建的局部海域水声信道测量平台(图 1),能够实现环境信息和信道参量的系统采集和实时传递,对信道

- 关键字:

设计 策略 系统 网络通信 浮标 TCP/IP

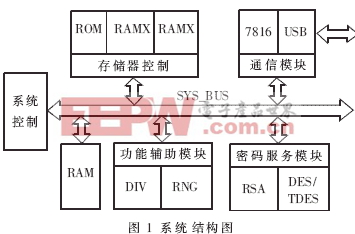

- 基于IP核及可重构设计的信息安全SoC芯片的实现,当前,信息安全防护已经从传统的单点信息加密发展到了以芯片级硬件防护为基础,构建覆盖全网络系统的信息保障体系。基于芯片级的硬件解决方案已经成为保证信息安全的最可靠的途径。可重构信息安全SoC芯片是基于信息安全

- 关键字:

SoC 芯片 实现 安全 信息 IP 重构 设计 基于

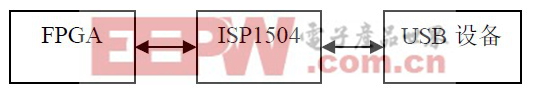

- USB2.0主机控制器IP核的设计,摘要 :为了摆脱对USB2.0 主机控制器ASIC 芯片的依赖,提高产品集成度,本文设计了针对全速和高速USB 海量存储设备的USB2.0 主机控制器IP 核。首先介绍USB2.0 主机控制器IP核中主要涉及的USB2.0 通信协议以及与物理层

- 关键字:

设计 IP 控制器 主机 USB2.0

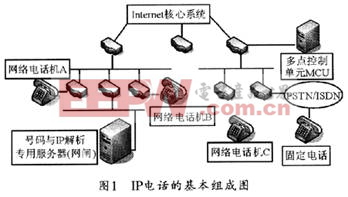

- 0 概述

IP电话以其通话费率低、方便集成和智能化等优势而得到了众多消费者的极大认可,并因此而对原有固定电话运营者的长途电话和国际电话业务造成了巨大冲击。因此,随着以太网接口的直接入户,开发出一种带有RJ-4

- 关键字:

系统 组成 原理 通信 电话 SIP 协议 IP 基于

- NGN业务具有端到端(Peer-to-Peer)及永久在线(Always-on-Line)的通信模式,需要分配大量IP地址,存在公网IP地址不足的问题。同时运营商在城域网中必须采用静态路由、动态路由、策略路由和路由策略等技术设置城域网路由

- 关键字:

设计 规划 路由 分配 IP 地址 NGN

designware ip介绍

您好,目前还没有人创建词条designware ip!

欢迎您创建该词条,阐述对designware ip的理解,并与今后在此搜索designware ip的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473