- 摘要:通用异步收发器UART常用于微机和外设之间的数据交换,针对UART的特点,提出了一种基于Ver4log HDL的UART设计方法。采用自顶向下的设计路线,结合状态机的描述形式,使用硬件描述语言设计UART的顶层模块及各个子

- 关键字:

Verilog UART HDL 模块设计

- 基于FPGA和DDS的信号源设计,1 引言

直接数字频率合成DDS(Direct Digital Synthesizer)是基于奈奎斯特抽样定理理论和现代器件生产技术发展的一种新的频率合成技术。与第二代基于锁相环频率合成技术相比,DDS具有频率切换时间短、频率分辨率

- 关键字:

设计 信号源 DDS FPGA 基于 FPGA,DDS,Verilog HDL

- Altium继续在其下一代电子产品设计软件Altium Designer中提供新功能,帮助电子产品设计人员站在新科技和潮流的最前沿。

Altium公司首席执行官Nick Martin表示:“我们认为,让用户等待每隔数年才更新一次版本的产业模型已经完全不符合当前的需求。”

此次最重要的新特性是基于网络的软件许可证管理和访问选项。它使电子产品设计人员能够有效地管理设计团队、工作量及项目。

Altium Designer中的其他新特性包括针对板卡级设计人员的定制FP

- 关键字:

Altium 电子产品设计 FPGA HDL

- 直接数字频率合成技术(Direct Digital Synthesize,DDS)是继直接频率合成技术和锁相式频率合成技术之后的第三代频率合成技术。它采用全数字技术,并从相位角度出发进行频率合成。随着微电子技术和数字集成电路的飞速

- 关键字:

Verilog HDL DDS 仿真

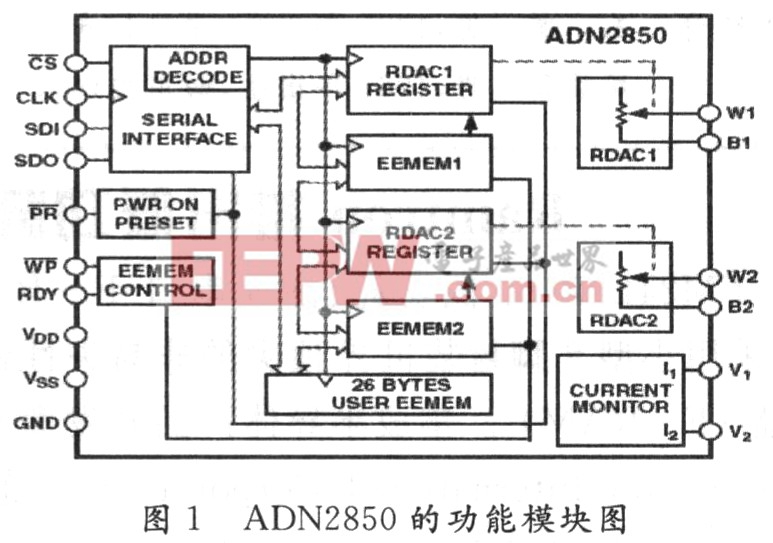

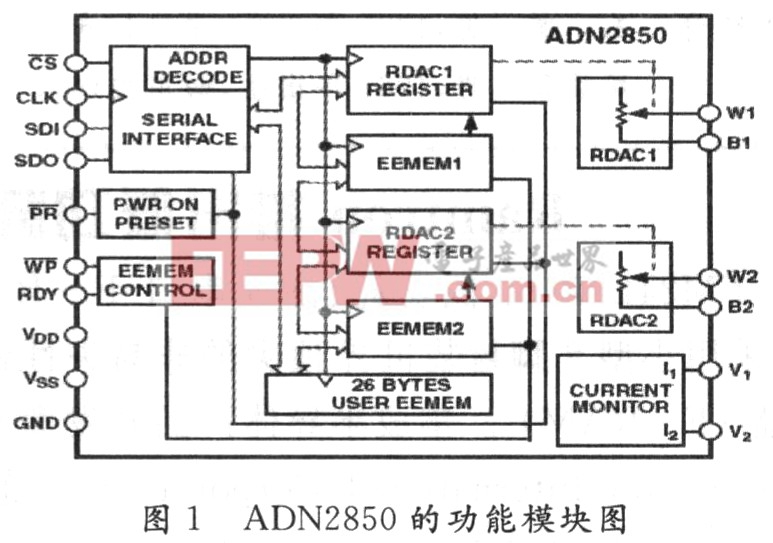

- 摘要:数字电位器由于可调精度高,更稳定,定位更准确,操作更方便,数据可长期保存和随时刷新等优点,在某些场合具有模拟电位器不可比拟的优势。论述对数字电位器ADN2850的一种方便的控制方法,通过计算机上的串口直

- 关键字:

串口 控制 ADN2850 数字电位器 Verilog HDL 基于

- 针对机器人伺服控制系统高速度、高精度的要求,介绍一种全数字化的基于神经网络控制的直流电机速度伺服控制系统的设计方案。速度控制器采用BP网络参数辨识自适应控制,并将其在FPGA进行硬件实现;同时用Nios II软核处理器作为上位机,构成一个完整的速度伺服控制器的片上可编程系统(SOPC)。实验结果表明,该控制系统具有较高的控制精度、较好的稳定性和灵活性。

- 关键字:

SOPC 系统 控制器 速度 神经网络 电机 基于 神经网络 伺服控制 现场可编程门阵列 Verilog HDL

- 随着集成电路制造技术的迅速发展,SOC设计已经成为当今集成电路设计的发展方向。SO C设计的复杂性对集成电路设计的各个层次,特别是对系统级芯片设计层次,带来了新挑战,原有的HDL难以满足新的设计要求。

硬件设计领域有2种主要的设计语言:VHDL和Verilog HDL。而两种语言的标准不统一,导致软硬件设计工程师之间工作交流出现障碍,工作效率较低。因此,集成电路设计界一直在寻找一种能同时实现较高层次的软件和硬件描述的系统级设计语言。Synopsys公司与Coware公司针对各方对系统级设计语言的

- 关键字:

SOC SystemC 集成电路 VHDL Verilog HDL

- 在现代IC设计中,特别是在模块与外围芯片的通信设计中,多时钟域的情况不可避免。当数据从一个时钟域传递到另一个域,并且目标时钟域与源时钟域不相关时,这些域中的动作是不相关的,从而消除了同步操作的可能性,并使系统重复地进入亚稳定状态[1]。在有大量的数据需要进行跨时钟域传输且对数据传输速度要求比较高的场合,异步FIFO是一种简单、快捷的解决方案。

异步FIFO用一种时钟写入数据,而用另外一种时钟读出数据。读写指针的变化动作由不同的时钟产生。因此,对FIFO空或满的判断是跨时钟域的。如何根据异步的指针

- 关键字:

FIFO 异步 Verilog HDL IC 亚稳态

- 一.可移植性编码

1.只使用IEEE标准类型(VHDL):(1)使用STD_LOGIC类型,而不是STD_ULOGIC类型;(2)设计中不要创建过多的的子类型;(3)不要使用BIT和BIT_VECTOR类型。

2.不使用立即数:在设计中,不要使用立即数(但作为例外,可使用0和1),推荐使用常量。使用常量有以下优点:(1)常量对于一个设计具有更多的灵活性;(2)常量值只需要在一个地方修改;(3)编译器可能只支持常量类型,不支持立即数。

3.对于VHDL程序,把常数和参数定义在由1个或多个文件组成的程序

- 关键字:

HDL 设计 可编程

- 1.引言

随着集成电路复杂度越来越高,测试开销在电路和系统总开销中所占的比例不断上升,测试方法的研究显得非常突出。目前在测试源的划分上可以采用内建自测试或片外测试。内建自测试把测试源和被测电路都集成在芯片的内部,对于目前SOC级的芯片测试如果采用内建自测试则付出的硬件面积开销则是很大的,同时也增加了芯片设计的难度:因此片外测试便成为目前被普遍看好的方法。由于FPGA具有可重构的灵活性,利用FPGA来作为测试源实现片外测试就是一种非常有效的手段。

由于伪随机模式测试只需要有限个数的输入向量便

- 关键字:

嵌入式系统 单片机 FPGA 序列生成器 Verilog HDL MCU和嵌入式微处理器

- 手机正在迈向多功能,一步紧跟潮流的手机除了通话,还可能集成调频收音、数码相机、移动电视、GPS、蓝牙、Wi-Fi甚至是WiMax。不同频段的电磁波涌向几寸见方的手机,信号的相互干扰导致信噪比下降,这已经是困扰所有手机芯片厂商的难题。加长高敏感信号接收器之间的距离在空间有限的手机上效果并不理想。从事噪音消除技术(Noise Cancellation)的Quellan公司开发出了一种噪音消除技术Q:ACTIVE,在手机接收端天线和LNA之间放置一个模拟IC,专门产生与预想噪音相反的信号,以此达到消除

- 关键字:

Quellan 噪音 Q:ACTIVE 模拟技术 消除噪音

- 摘 要:本论文介绍视频编解码IP核在SOPC中的设计,用Verliog HDL实现其各个功能子模块,全部调试仿真通过合并成一个模块,实现了视频信号的采集,分配,存储以及色度空间的转换。整个模块都通过仿真实现与验证,很好的达到了系统的要求。关键字:SOPC;视频编解码;IP核;Verilog HDL 引言 基于Nios II软核的SOPC是Altera公司提出的片上可编程系统解决方案,它将CPU、存储器、I/O接口、DSP模块以及锁相环的系统设

- 关键字:

嵌入式系统 单片机 SOPC 频编解码 SOPC 视频编解码 IP核 Verilog HDL

- 引言:数字滤波器是语音与图像处理、模式识别、雷达信号处理、频谱分析等应用中的一种基本的处理部件,它能满足波器对幅度和相位特性的严格要求,避免模拟滤波器所无法克服的电压漂移、温度漂移和噪声等问题。有限冲激响应(FIR)滤波器能在设计任意幅频特性的同时保证严格的线性相位特性。

一、FIR数字滤波器

FIR滤波器用当前和过去输入样值的加权和来形成它的输出,如下所示的前馈差分方程所描述的。

FIR滤波器又称为移动均值滤波器,因为任何时间点的输出均依赖于包含有最新的M个输入样值的一个窗。

- 关键字:

嵌入式系统 单片机 Verilog HDL FIR 数字滤波器 嵌入式

- 第一部分:说明

1.准则的重要程度分三个层次:

好的经验 -- 表明这条规则是一般情况下比较好的经验,在大多数的情况下要遵循,在特殊情况下可以突破这一规则。

推荐 -- 推荐这一规则,在遵循这一规则的条件下,一般不会出现问题;

强烈推荐 -- 表示严格规定,除非出现特别特殊的情况,否则要严格遵守。

2.斜体部分一般表明不按照规则执行,会出现的问题和现象,或一些相关注释。

3.版本及修订工作

姓名 徐欣,孙广富

修订 规范的最初发布

日期 2002-6-30

- 关键字:

HDL 编码风格 编码指南 嵌入式

active-hdl介绍

您好,目前还没有人创建词条active-hdl!

欢迎您创建该词条,阐述对active-hdl的理解,并与今后在此搜索active-hdl的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473